# UNIVERSIDADE FEDERAL RURAL DO SEMI-ÁRIDO PRÓ-REITORIA DE PESQUISA E PÓS-GRADUAÇÃO PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA MESTRADO EM ENGENHARIA ELÉTRICA

WISLA MILENA MORAIS DE OLIVEIRA

RECEPTOR DE CONVERSÃO DIRETA INTEGRADO EM TECNOLOGIA CMOS PARA APLICAÇÕES DE ULTRA BAIXO CONSUMO

MOSSORÓ

# WISLA MILENA MORAIS DE OLIVEIRA

# RECEPTOR DE CONVERSÃO DIRETA INTEGRADO EM TECNOLOGIA CMOS PARA APLICAÇÕES DE ULTRA BAIXO CONSUMO

Dissertação de mestrado apresentada ao Programa de Pós-graduação em Engenharia Elétrica da Universidade Federal Rural do Semi-árido (UFERSA) como requisito parcial para obtenção do título de Mestre em Engenharia Elétrica.

Linha de Pesquisa: Telecomunicações e Eletromagnetismo Aplicado

Orientador: Francisco de Assis Brito Filho, Prof. Dr.

MOSSORÓ

© Todos os direitos estão reservados a Universidade Federal Rural do Semi-Árido. O conteúdo desta obra é de inteira responsabilidade do (a) autor (a), sendo o mesmo, passível de sanções administrativas ou penais, caso sejam infringidas as leis que regulamentam a Propriedade Intelectual, respectivamente, Patentes: Lei nº 9.279/1996 e Direitos Autorais: Lei nº 9.610/1998. O conteúdo desta obra tomar-se-á de domínio público após a data de defesa e homologação da sua respectiva ata. A mesma poderá servir de base literária para novas pesquisas, desde que a obra e seu (a) respectivo (a) autor (a) sejam devidamente citados e mencionados os seus créditos bibliográficos.

OO48r Oliveira, Wisla Milena Morais de.

RECEPTOR DE CONVERSÃO DIRETA INTEGRADO EM

TECNOLOGIA CMOS PARA APLICAÇÕES DE ULTRA BAIXO

CONSUMO / Wisla Milena Morais de Oliveira. - 2023.

84 f.: il.

Orientador: Francisco de Assis Brito-Filho. Dissertação (Mestrado) - Universidade Federal Rural do Semi-árido, Programa de Pós-graduação em Engenharia Elétrica, 2023.

1. Portabilidade . 2. Sensibilidade. 3. CMOS. 4. Baixo consumo. 5. Receptores de conversão direta. I. Brito-Filho, Francisco de Assis , orient. II. Título.

Ficha catalográfica elaborada por sistema gerador automáto em conformidade com AACR2 e os dados fornecidos pelo) autor(a).

Biblioteca Campus Mossoró / Setor de Informação e Referência

Bibliotecária: Keina Cristina Santos Sousa e Silva

CRB: 15/120

O serviço de Geração Automática de Ficha Catalográfica para Trabalhos de Conclusão de Curso (TCC´s) foi desenvolvido pelo Instituto de Ciências Matemáticas e de Computação da Universidade de São Paulo (USP) e gentilmente cedido para o Sistema de Bibliotecas da Universidade Federal Rural do Semi-Árido (SISBI-UFERSA), sendo customizado pela Superintendência de Tecnologia da Informação e Comunicação (SUTIC) sob orientação dos bibliotecários da instituição para ser adaptado às necessidades dos alunos dos Cursos de Graduação e Programas de Pós-Graduação da Universidade.

# WISLA MILENA MORAIS DE OLIVEIRA

# RECEPTOR DE CONVERSÃO DIRETA INTEGRADO EM TECNOLOGIA CMOS PARA APLICAÇÕES DE ULTRA BAIXO CONSUMO

Dissertação de mestrado apresentada ao Programa de Pós-graduação em Engenharia Elétrica da Universidade Federal Rural do Semi-árido (UFERSA) como requisito parcial para obtenção do título de Mestre em Engenharia Elétrica.

Orientador: Francisco de Assis Brito Filho, Prof. Dr.

Defendida em: 23 de Fevereiro de 2023.

#### BANCA EXAMINADORA

Francisco de Assis Brito Filho, Prof. Dr. Presidente da Banca e Orientador

Humberto Dionísio de Andrade, Prof. Dr. Membro Interno

Diomadson Rodrigues Belfort, Prof. Dr. Membro externo

MOSSORÓ

2023

# **AGRADECIMENTOS**

Inicio agradecendo ao bom Deus pelo fôlego de vida, pela oportunidade de cursar uma pósgraduação, por seu meu guia em todo o tempo e pelas pessoas que colocou em meu caminho para me ajudar chegar até aqui.

À minha família, por ser minha base e apoio em todas as circunstâncias. Gratidão especial a minha mãe, Girlene Maria de Morais que não mede esforços em me ajudar.

Ao meu orientador Francisco Brito Filho pelos ensinamentos, palavras positivas, conselhos e críticas construtivas.

Ao corpo docente da UFERSA pelas experiências repassadas.

Aos meus amigos pelo apoio e a todos que direta ou indiretamente me ajudaram.

À CAPES, pelo auxílio financeiro.

#### **RESUMO**

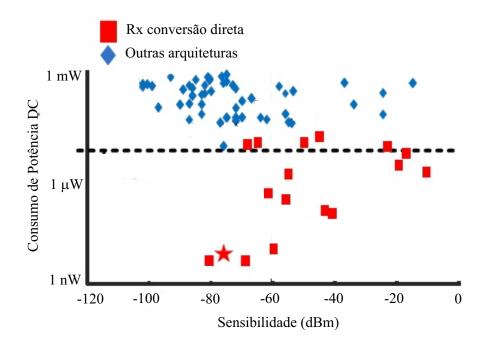

No desenvolvimento de dispositivos portáteis e com vida útil elevada, o baixo consumo de energia e a miniaturização são características essenciais. Essas características são demandadas em aplicações modernas nas mais diversas áreas, como por exemplo, sistemas biomédicos para monitoramento de anomalias e dispositivos de comunicação sem fio para Internet das coisas. No que se refere ao projeto de receptores de radio frequência, existe um compromisso entre a sensibilidade do receptor e o consumo de energia. Nesse contexto, esta pesquisa avalia a sensibilidade de um receptor de conversão direta CMOS utilizando circuitos de baixo consumo. Os circuitos discutidos para o cálculo da sensibilidade são um detector de envelope do tipo passivo e um amplificador com acoplamento CA. Os blocos do receptor foram implementados utilizando os modelos e fluxos de projeto das tecnologias CMOS SkyWater 130 nm e UMC 180 nm, para prototipagem de um ASIC, o que agrega portabilidade e miniaturização a arquitetura proposta. Para a tecnologia SkyWater o fluxo de projeto totalmente open-source é utilizado. Com os resultados simulados foi obtida uma sensibilidade de  $-58,7 \, dBm$  com um consumo de  $0.9 \,\mu W$  para a tecnologia UMC 180 nm e uma sensibilidade de  $-64.7 \,dBm$  com um consumo de 1,8 μW para a tecnologia SkyWater 130 nm. Considerando a relação entre consumo de energia e sensibilidade, os resultados alcançados nessa pesquisa são comparados com os do estado da arte.

**Palavras-chave:** Portabilidade. Sensibilidade. CMOS. Baixo consumo. Receptores de conversão direta.

#### **ABSTRACT**

In developing portable devices with long useful life, low power consumption and miniaturization are essential features. These characteristics are required in modern applications in several areas, such as biomedical systems for monitoring anomalies and wireless communication devices for Internet of Things. Concerning the radiofrequency receiver design, there is a trade off between sensitivity of the receiver and power consumption. The circuits discussed for the sensitivity calculation are a passive-type envelope detector and an AC-coupled amplifier. Receiver blocks have been implemented using the models and design flows of CMOS technologies SkyWater 130 nm and UMC 180 nm, for prototyping an ASIC, which adds portability and miniaturization to the architecture proposal. For the SkyWater technology, a fully open-source design flow was used. With the simulated results, a sensitivity of  $-58.7 \, dBm$  was obtained with a power consumption of  $0.9 \, \mu W$  for the UMC 180 nm technology and a sensitivity of  $-64.7 \, dBm$  with a consumption of  $1.8 \, \mu W$  for the technology SkyWater 130 nm. Considering the compromise between power consumption and sensitivity, the results achieved in this research are compared with those of the state of the art.

**Keywords:** Portability. Sensitivity. CMOS. Low-consumption. Direct-conversion receivers.

# LISTA DE ILUSTRAÇÕES

| Figura 1 – Diagrama de blocos de receptor heteródino.                                           | 19 |

|-------------------------------------------------------------------------------------------------|----|

| Figura 2 - Trade-off entre filtro de seleção de canal e filtro de rejeição de imagem            | 20 |

| Figura 3 – Arquitetura de receptores.                                                           | 22 |

| Figura 4 – Comparativo entre receptores encontrados na literatura                               | 23 |

| Figura 5 – Detector de envoltória com Mosfet conectado como diodo                               | 24 |

| Figura 6 – Topologia de detectores.                                                             | 24 |

| Figura 7 – Arquitetura de amplificador com acoplamento AC                                       | 25 |

| Figura 8 – Arquitetura de OTAs                                                                  | 27 |

| Figura 9 – Funcionamento de um comparador sem histerese.                                        | 28 |

| Figura 10 – Principio de funcionamento de um comparador com histerese                           | 29 |

| Figura 11 – Ilustração do Funcionamento da Modulação Digital ASK                                | 30 |

| Figura 12 – Ilustração da largura de banda equivalente do ruído                                 | 31 |

| Figura 13 – Blocos em cascata.                                                                  | 32 |

| Figura 14 – Diagrama de blocos do sistema proposto                                              | 34 |

| Figura 15 – Esquemático do detector de Envelope.                                                | 35 |

| Figura 16 – Configuração do amplificador com acoplamento AC com fonte simples                   | 36 |

| Figura 17 – Arquitetura do pseudo resistor.                                                     | 37 |

| Figura 18 – Conexão entre o comparador e o FPGA                                                 | 38 |

| Figura 19 – Etapas para a realização da pesquisa                                                | 39 |

| Figura 20 – Fluxo de projeto de um ASIC analógico e as ferramentas em cada fase                 | 40 |

| Figura 21 – Fluxo de projeto de um ASIC digital e as ferramentas <i>open-source</i> utilizadas. | 41 |

| Figura 22 – Harness Caravel                                                                     | 43 |

| Figura 23 – Ilustração da integração com a <i>Harness</i>                                       | 43 |

| Figura 24 – Fluxo de projeto de ASIC com UMC e ferramentas <i>Cadence</i>                       | 44 |

| Figura 25 – Plano de testes.                                                                    | 45 |

| Figura 26 – Análise transiente do detector para tecnologia <i>SkyWater</i> 130 nm               | 48 |

| Figura 27 – Densidade espectral de potência do ruído na saída do detector                       | 49 |

| Figura 28 – Ganho de conversão para o detector da tecnologia <i>SkyWater</i>                    | 50 |

| Figura 29 – <i>Layout</i> do detector de envelope.                                              | 50 |

| Figura 30 – Comparativo do ruído de saída pré e pós- <i>layout</i>                              | 51 |

| Figura 31 – Resultados pré e pós- <i>layout</i> para o ganho de conversão                       | 52 |

| Figura 32 – Análise transiente do detector para tecnologia UMC 180 nm                           | 53 |

| Figura 33 – Ruído na saída do detector da tecnologia UMC 180 nm.                                | 53 |

| Figura 34 – Ganho de conversão para o detector da tecnologia UMC 180 nm                         | 54 |

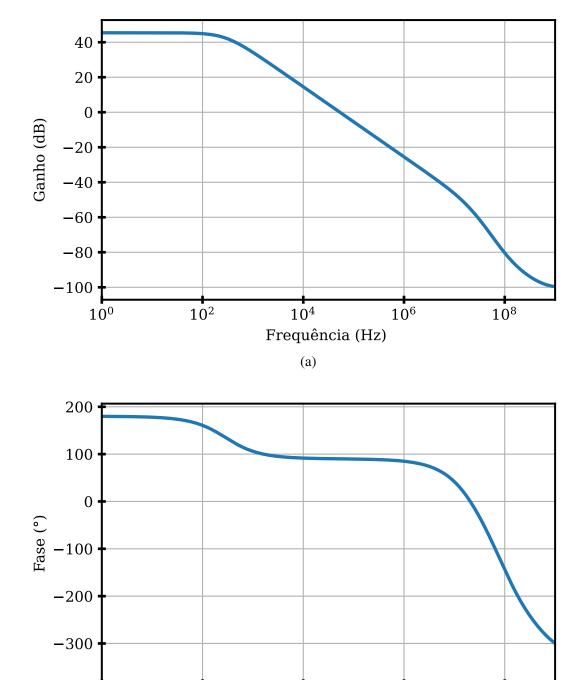

| Figura 35 – Resposta AC em malha aberta para OTA da UMC 180 nm                                  | 56 |

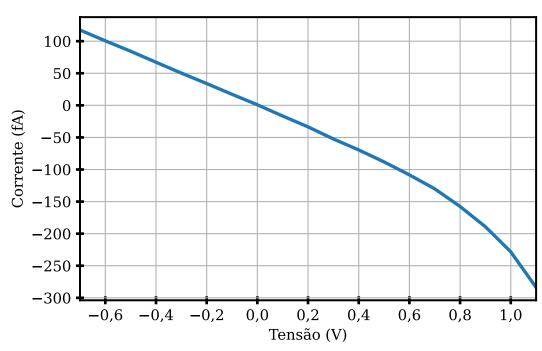

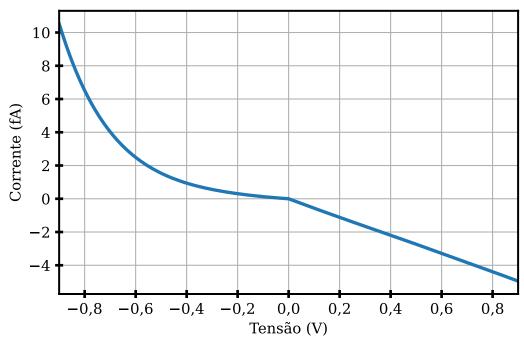

| Figura 36 – Gráfico da tensão <i>versus</i> corrente do pseudo-resistor com a <i>SkyWater</i>   | 57 |

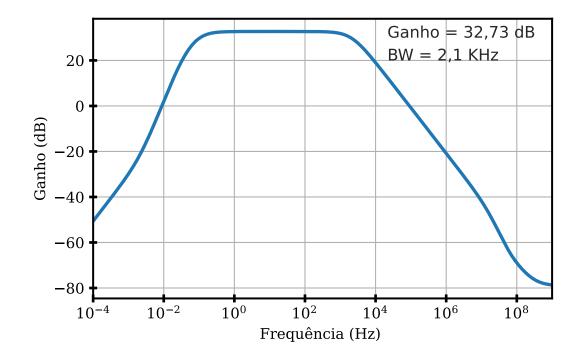

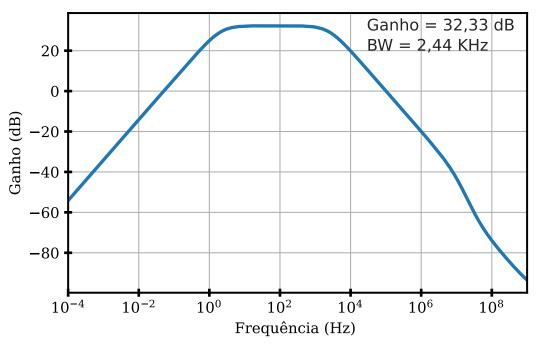

| Figura 37 – Ganho em malha fechada do amplificador.                                  | 59 |

|--------------------------------------------------------------------------------------|----|

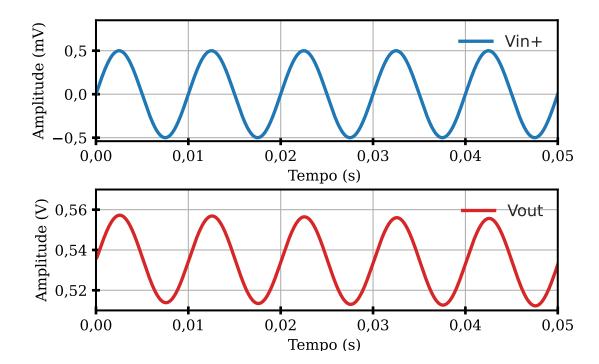

| Figura 38 – Análise Transiente do amplificador.                                      | 60 |

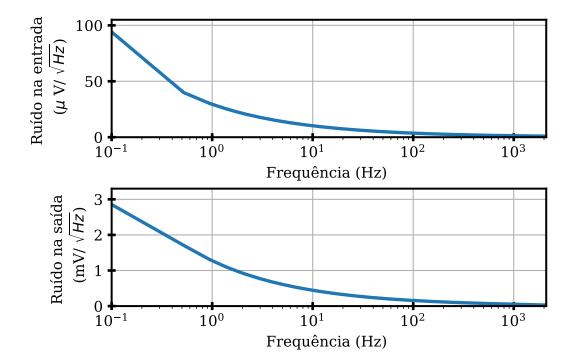

| Figura 39 – Ruído do amplificador.                                                   | 61 |

| Figura 40 – Layout do OTA feito no Magic Layout.                                     | 62 |

| Figura 41 – Resposta AC pós- <i>layout</i> .                                         | 63 |

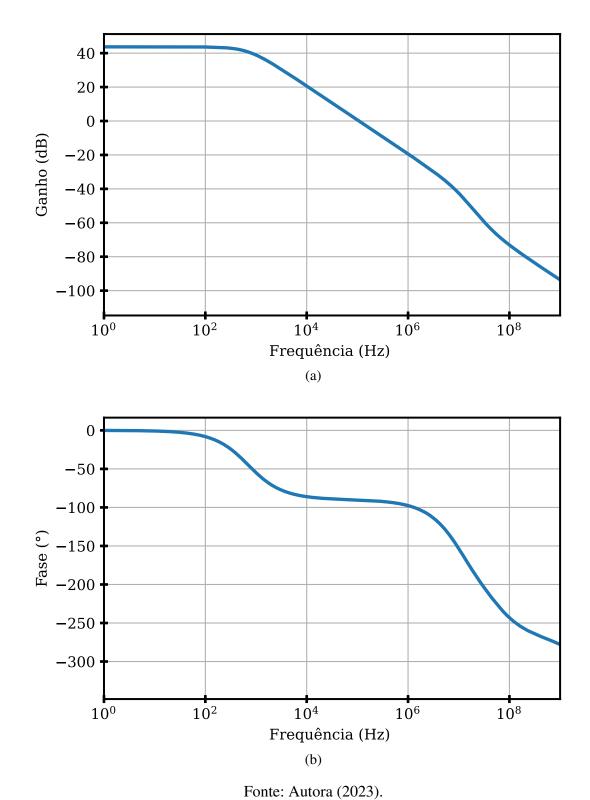

| Figura 42 — Análise AC em malha aberta para UMC: (a) Ganho do OTA e (b) Fase do OTA. | 65 |

| Figura 43 – Gráfico da tensão <i>versus</i> corrente do pseudo resistor UMC.         | 66 |

| Figura 44 – Ganho em malha fechada.                                                  | 67 |

| Figura 45 – Análise Transiente do amplificador para tecnologia UMC 180 nm            | 68 |

| Figura 46 – Análise de ruído do amplificador para tecnologia UMC 180 nm              | 69 |

| Figura 47 – Ganho de conversão para o detector de envelope.                          | 71 |

| Figura 48 – Ganho de conversão para o detector de envelope.                          | 72 |

| Figura 49 – Resultados de sensibilidade para tecnologia <i>SkyWater</i> 130nm        | 73 |

| Figura 50 – Resultados de sensibilidade para tecnologia UMC 180nm.                   | 74 |

| Figura 51 – Simulação do MODEM ASK.                                                  | 75 |

| Figura 52 – <i>Trade-off</i> entre sensibilidade e consumo de energia                | 76 |

|                                                                                      |    |

# LISTA DE TABELAS

| Tabela 1 – Dimensões dos transistores do OTA para <i>SkyWater</i> 130 nm       | 55 |

|--------------------------------------------------------------------------------|----|

| Tabela 2 – Valores de resistência simulados                                    | 58 |

| Tabela 3 – Comparativo dos resultados pré e pós- <i>layout</i> do OTA          | 64 |

| Tabela 4 – Dimensões dos transistores do OTA espelho de corrente da UMC 180 nm | 64 |

| Tabela 5 – Valores de resistência simulados para UMC                           | 66 |

| Tabela 6 – Comparativo entre os resultados do amplificador                     | 70 |

| Tabela 7 – Comparação dos receptores encontrados no estado da arte             | 76 |

#### LISTA DE ABREVIATURAS E SIGLAS

ampOp Amplificador Operacional

ADC Converso analógico-digital, do inglês *Analog-to-Digital Converter*

ASIC Application-Specific Integrated Circuit

ASK Amplitude Shift Keying

BB Banda Base

BW largura da banda passante, do inglês Bandwidth

CG Ganho de Conversão, do inglês conversion gain

CI Circuito Integrado

CMOS Complementary Metal-Oxide Semiconductor

CMRR Razão de Rejeição de Modo Comum, do inglês Common Mode Rejection

Ratio

dB Unidade de tensão ou potência em Decibel

dBm Decibel-miliwatts

DRC Termo do inglês Design Rules Check

EDA Eletronic Design Automation

ENBW Largura de banda de ruído equivalente, do inglês *Equivalent noise bandwidth*

FPGA Matriz de portas programáveis em campo, do inglês Field-Programmable

Gate Array

GBW Produto ganho-banda, do inglês Gain-bandwidth product

GDS II Formato padrão de arquivo da indústria de circuitos integrados, sigla para o

termo Graphic Data System

GPIO Pinos de entrada e saída para propósitos gerais, do inglês (General-Purpose

Input-Output

GPS Sistema de Posicionamento Global, do inglês *Global Positioning System*

IF Frequência intermediária, do inglês *Intermediate Frequency*

IOT Internet das Coisas, do inglês Internet of Things

ISM faixas de frequências reservadas para desenvolvimento industrial, médico e

científico (do inglês Industrial Scientific and Medical)

LNA Amplificador de baixo ruído, do inglês Low-Noise Amplifier

LO Oscilador local, do inglês *Local-Oscilator*

LVS do inglês, Layout versus Schematic

MODEM Modulador-Demodulador

MPW do inglês Multi-project wafer

NEF Fator de Eficiência do Ruído, do inglês *Noise Efficiency Factor*

NF Figura de ruído, do inglês *Noise Figure*

NMOS Transistor de efeito de campo metal-óxido-semicondutor do tipo N

OOK ON-OFF Keying

OTA Amplificador operacional de transcondutância, do inglês *Operational Trans*-

conductance Amplifier

PDK do inglês *Process design kit*

PMOS Transistor de efeito de campo metal-óxido-semicondutor do tipo P

PSD Power Spectral Density

PSOC Sistema em um Chip programável, do inglês *Programmable System on Chip*

RF Radiofrequência

RMS do inglês *Root Mean Square*

RTL do inglês Register Transfer Level

Rx Taxa de recepção de dados

SNR Relação entre sinal e ruído, do inglês Signal-to-Noise Ratio

SoC Sistem em um chip, do inglês *System on a chip*

THD Distorção harmônica total do inglês *Total harmonic distortion*

Tx Taxa de transmissão de dados

VHDL do inglês VHSIC Hardware Description Language

WLAN Rede Local Sem Fios, do inglês Wireless Local Area Network

# LISTA DE SÍMBOLOS

Ac Ganho de modo comum

Ad Ganho diferencial

AM Ganho de banda passante

Cl Capacitor de carga

$\Delta R$  Parâmetro de variabilidade do Pseudo-Resistor

F Fator de ruído, do inglês *Noise Factor*

$F_c$  Frequência de corte

$F_{3dB}$  Frequência em -3 dB

$f_H$  Frequência de corte superior

$f_L$  Frequência de corte inferior

gds Condutância de saída

gm transcondutância do transistor

*i<sub>BIAS</sub>* Corrente de polarização

$I_D$  Corrente de dreno

k Constante de Boltzmann

L Comprimento do canal

NO Ruído total na saída

NS Ruído térmico do resistor

T Temperatura em *Kelvin*

VB Tensão de polarização

VBS Tensão substrato-fonte

VCM Tensão de modo comum

VDS Tensão dreno-fonte

VGS Tensão porta-fonte ou tensão entre *gate* e o *source* do transistor

Vov Tensão de *overdriver*

$V_R$  Tensão de referência do comparador *Schmitt trigger*

Vth Tensão de limiar, do inglês *Threshold voltage*

$V_{TH}$  Tensão de limiar superior do comparador

$V_{TL}$  Tensão de limiar inferior do comparador

W Largura do transistor

$\omega$  Frequência angular obtida pela relação  $2\pi f$

# SUMÁRIO

| 1     | INTRODUÇÃO                                                   | 16         |

|-------|--------------------------------------------------------------|------------|

| 1.1   | Objetivo geral                                               | 17         |

| 1.2   | Objetivos específicos                                        | 17         |

| 1.3   | Justificativa                                                | 18         |

| 1.4   | Estrutura da dissertação                                     | 18         |

| 2     | REFERENCIAL TEÓRICO                                          | 19         |

| 2.1   | Arquiteturas de Receptores                                   | 19         |

| 2.2   | Receptores de Baixo Consumo                                  | 21         |

| 2.3   | Sensibilidade                                                | 30         |

| 2.4   | Resumo do capítulo                                           | 33         |

| 3     | SISTEMA PROPOSTO E METODOLOGIA                               | 34         |

| 3.1   | Sistema Proposto                                             | 34         |

| 3.2   | Metodologia                                                  | 38         |

| 3.2.1 | Fluxo de Projeto Open-source                                 | 40         |

| 3.2.2 | Fluxo de Projeto com ferramentas da Cadence                  | 44         |

| 3.2.3 | Setup para teste experimental dos ASICs                      | 45         |

| 3.3   | Resumo do capítulo                                           | 46         |

| 4     | RESULTADOS E DISCUSSÕES                                      | 47         |

| 4.1   | Detector de Envelope                                         | 47         |

| 4.1.1 | Resultados para a tecnologia CMOS SkyWater 130 nm            | 47         |

| 4.1.2 | Resultados com a tecnologia CMOS UMC 180 nm                  | 52         |

| 4.1.3 | Discussões a respeito dos resultados do detector de envelope | 54         |

| 4.2   | Amplificador com acoplamento CA                              | 55         |

| 4.2.1 | Resultados para a tecnologia CMOS SkyWater 130 nm            | 55         |

| 4.2.2 | Resultados para a tecnologia CMOS UMC 180nm                  | 64         |

| 4.2.3 | Discussões sobre os resultados do amplificador               | 69         |

| 4.3   | Figura de ruído e Sensibilidade                              | <b>7</b> 0 |

| 4.4   | MODEM ASK                                                    | 74         |

| 4.5   | Análise da Sensibilidade versus Consumo de Energia           | 75         |

| 4.6   | Resumo do capítulo                                           | 77         |

| 5     | CONCLUSÕES                                                   | 78         |

| 5.1   | Perspectivas para trabalhos futuros                          | <b>7</b> 9 |

|       | REFERÊNCIAS                                                  | 80         |

# 1 INTRODUÇÃO

Reduzir o consumo de energia é um requisito fundamental em sistemas onde se busca portabilidade e uma longa vida útil. Essa redução de consumo deve ser examinada tanto em nível de *hardware* quanto em nível de *software* (KAMALINEJAD et al., 2014). De acordo com Wentzloff et al. (2021), na análise do consumo de energia de sistemas Internet das coisas (IOT, do inglês *Internet Of Things*) a maior parte da energia é gasta nos sistemas de comunicação sem fio e reduzir o consumo desses sistemas é desejável.

No entanto, essa necessidade de sistemas com baixo consumo se estende a aplicações com sensores inteligentes, rede sensores sem fio, dispositivos vestíveis e sistemas de monitoramento de cuidados com a saúde (CHENG; CHEN, 2017; VIANA; BELFORT, 2019; YAN et al., 2018). Com o advento e desenvolvimento dessas aplicações modernas, o consumo de energia dos sistemas de comunicação é uma métrica importante, haja vista que esses sistemas podem ser determinantes para a redução do consumo total de energia.

Aprofundando mais sobre os sistemas de comunicação, estes estão presentes assiduamente na nossa rotina, nesse sentido, os autores em Wentzloff et al. (2021) estimando uma quantidade de 1 trilhão de dispositivos sem fio conectados, apontam que esses dispositivos com baterias de vida útil pequena, além de apresentarem a necessidade de recorrente manutenção ou troca de bateria, acarretam impactos ao meio ambiente em virtude do descarte das baterias, que segundo o autor, nos sistemas de IOT, possuem uma vida útil média de três anos.

Com relação aos circuitos de recepção de sinais, existe um *trade-off* entre consumo de energia e o mínimo sinal detectável. Via de regra, um menor sinal detectável é alcançado em sistemas com maior consumo de energia. No entanto, progressos direcionados no desenvolvimento de circuitos com baixo consumo tem possibilitado a redução do gasto energético com melhoria do mínimo sinal detectável do receptor (MOODY et al., 2019). A escolha da arquitetura do receptor também deve ponderar aspectos como custo e complexidade (RAZAVI, 2012).

As arquiteturas de receptores de radiofrequência (RF) podem ser classificadas em dois tipos principais, a saber, heteródino e homódino. O primeiro tipo faz o processo de conversão da frequência RF para uma frequência intermediária e posteriormente recupera o sinal banda base, enquanto os homodinos fazem a conversão em uma única etapa e por isso também são chamados de receptores de conversão direta. Os receptores de conversão direta destacam-se dos tradicionais heteródinos quando o objetivo é reduzir complexidade e consumo (MOODY et al., 2019). Ainda segundo Razavi (2012) esses receptores tem ganhado espaço desde os anos 2000 em virtude das melhorias de integração e sofisticação dessas arquiteturas simples.

Nesse contexto, também pode ser agregado a importância da miniaturização e consequente portabilidade do sistema de recepção, como uma característica atrativa para as aplicações

de comunicação sem fio. Com a finalidade de avaliar a melhoria do mínimo sinal detectável para um receptor de ultra-baixo consumo, esta pesquisa propõe a implementação de um receptor de conversão direta integrado em tecnologia CMOS (do inglês, *Complementary metal-oxide-semiconductor* cuja tradução seria semicondutor de óxido metálico complementar).

O desenvolvimento do receptor em tecnologia CMOS tem como resultado final um circuito integrado para aplicação específica (ASIC, do inglês *Application-Specific Integrated Circuit*). Nos últimos anos, tem-se observado um crescente incentivo à democratização do conhecimento a respeito do fluxo de projeto de ASICs. Desde 2020, a *SkyWater* em colaboração com a *Google* e intermediação da *Efabless corporation* tornaram acessível o desenvolvimento ponta a ponta de um ASIC de forma gratuita (PAJKANOVIC, 2021; EDWARDS; SHALAN; KASSEM, 2021; *EFABLESS CORPORATION*, c2022). Além desse programa *open-source*, a EUROPRACTICE oferece baixo custo para fabricação de ASICs para verificação inicial (DAS; MCLEAN, 2003). Essas iniciativas também agregam motivação ao desenvolvimento dessa pesquisa.

Considerando os pressupostos destacados, a importância de buscar soluções com baixo consumo para as aplicações atuais e as oportunidades de pesquisa no desenvolvimento de ASICs, esse trabalho propõe o desenvolvimento de um receptor de conversão direta integrado em tecnologia CMOS de 130 e 180 nm, com ênfase na verificação de um detector de envelope passivo e um amplificador com acoplamento capacitivo, de ultra-baixo consumo, como meio para melhorar a sensibilidade.

# 1.1 Objetivo geral

O objetivo geral dessa pesquisa é desenvolver o circuito integrado de um receptor de conversão direta composto por um detector de envelope passivo e um amplificador com acoplamento capacitivo de ultra-baixo consumo, como método para melhorar a sensibilidade do receptor.

# 1.2 Objetivos específicos

Para alcançar o objetivo geral, os seguintes objetivos específicos são propostos:

- Realizar o levantamento bibliográfico sobre receptores de baixo consumo.

- Projetar os blocos do receptor, priorizando os circuitos com menor consumo de energia.

- Criar um esquema de simulação que permita a validação dos subsistemas criados.

- Quantificar a sensibilidade da solução proposta e comparar com as do estado da arte, ponderando os *trade-offs* em relação ao consumo de energia.

- Elaborar e submeter para fabricação, um ASIC com os blocos analógicos e digitais projetados.

- Desenvolver algoritmos em linguagem de descrição de hardware para implementação dos módulos digitais em dispositivo de lógica programável (FPGA – Field Programmable Gate Array).

#### 1.3 Justificativa

Considerando a importância de circuitos de baixo consumo para as aplicações com sistemas de transmissão e recepção de sinais, essa pesquisa busca contribuir com o estado da arte através da proposta de uma arquitetura de receptor com ultra-baixo consumo. Dentre as aplicações com necessidade de componentes com baixo consumo pode-se referenciar, IOT, rede de sensores sem fio, dispositivos emergentes para monitoramento de cuidados com a saúde e dispositivos vestíveis (WENTZLOFF et al., 2021; YAN et al., 2018; KAMALINEJAD et al., 2014).

Avaliando a recorrente necessidade de técnicas para redução de consumo e o *trade-off* existente entre mínimo sinal detectável e consumo de energia, técnicas para melhorar a sensibilidade do receptor são benéficas no projeto de dispositivos de comunicação sem fio. Essa pesquisa surge da percepção da crescente demanda por sistemas que além do baixo consumo e bom desempenho, agreguem simplicidade, baixo custo, miniaturização e consequentemente portabilidade as aplicações que requerem tais especificações.

# 1.4 Estrutura da dissertação

Esta dissertação está dividida em cinco capítulos. O presente capítulo apresentou uma breve contextualização a respeito da temática principal, exibindo como situar a proposta do trabalho com as aplicações mais recentes da literatura. O capítulo 2 exibirá uma revisão bibliográfica sobre os tipos de receptores e as soluções demonstradas na literatura para o *design* de um receptor com baixo consumo de energia, bem como as equações para cálculo da sensibilidade. O sistema proposto e a metodologia empregada serão discutidos no capítulo 3 e o capítulo 4 apresentará os resultados obtidos. Por fim, após a exposição dos resultados, o capítulo 5 abordará as considerações finais sobre o trabalho e as perspectivas futuras para continuação dessa pesquisa.

# 2 REFERENCIAL TEÓRICO

Neste capítulo será abordado sobre as arquiteturas de receptores heteródino e homódino, descrevendo as principais características e as métricas de baixo consumo de energia e sensibilidade para essas arquiteturas. Uma revisão sobre receptores propostos na literatura para aplicações de baixo consumo será discutida, além da equação para quantificação da sensibilidade e os parâmetros que à influenciam.

# 2.1 Arquiteturas de Receptores

As arquiteturas de receptores podem ser classificadas de acordo com o processo de conversão de frequência em dois tipos principais: receptores heteródinos e receptores homódinos. A Figura 1 mostra o diagrama de blocos de uma arquitetura de receptor heteródino.

Sinal RF

Filtro rejeita imagem

Sinal IF

Filtro seleção de canal

Figura 1 – Diagrama de blocos de receptor heteródino.

Fonte: Autora (2023).

Em um bloco receptor, uma etapa de conversão ou tradução deve ser realizada para obter o sinal da informação que foi modulado no transmissor. O bloco misturador realiza essa função. Em um receptor do tipo heteródino, o sinal RF é convertido para uma frequência intermediária (IF, do inglês *Intermediate Frequency*) e posteriormente um bloco de demodulação recupera o sinal banda base. O misturador realiza essa conversão com auxílio de um oscilador local (LO, do inglês *Local Oscillator*) e a frequência intermediária é obtida por meio da multiplicação entre o sinal de entrada e o sinal gerado pelo oscilador (RAZAVI, 2012).

Esse processo de conversão no entanto, gera o problema conhecido como problema da imagem. Uma vez que o sinal gerado pelo o oscilador possui uma função do tipo  $A\cos\omega_{LO}t$ , duas frequências distintas podem produzir o mesmo IF (LEE, 2004; RAZAVI, 2012). Matematicamente, isso pode ser explicado pela equação (2.1) (RAZAVI, 2012).

$$A\cos\omega_{If} t = A\cos(\omega_{in} - \omega_{LO})t = A\cos(\omega_{LO} - \omega_{in})t$$

(2.1)

Percebe-se que tanto o valor positivo quanto o valor negativo de  $(\omega_{LO} - \omega_{in})$  pode produzir a mesma frequência IF e em virtude da simetria entre essas componentes de frequência, uma é chamada de imagem da componente desejada (RAZAVI, 2012). Para resolver esse problema, um filtro para rejeição de imagem é utilizado antes do misturador (LEE, 2004).

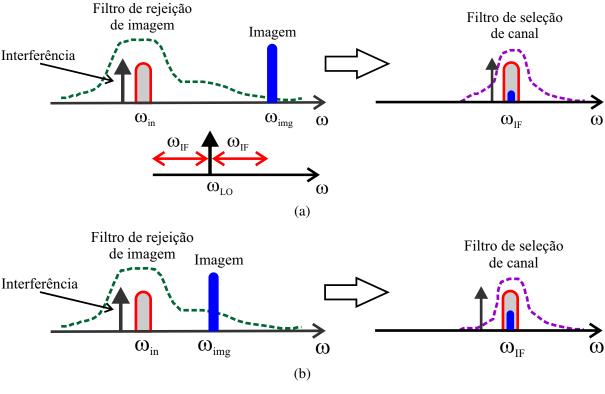

Além do problema da imagem, existe um *trade-off* na escolha da frequência intermediária. A Figura 2 ilustra esse *trade-off* indicando as componentes de frequência para um valor baixo ou alto de IF e o processo de filtragem. Na ilustração  $\omega_{in}$  é a frequência do sinal desejado,  $\omega_{img}$  a frequência da imagem,  $\omega_{LO}$  a frequência gerada pelo oscilador e  $\omega_{IF}$  a frequência intermediária.

Figura 2 – *Trade-off* entre filtro de seleção de canal e filtro de rejeição de imagem: (a) IF alto; (b) IF baixo.

Fonte: Autora (2023).

Considerando um valor alto da IF, o *design* do filtro de rejeição de imagem possuirá menos restrições, contudo o filtro de seleção de canal será projetado considerando frequências mais altas com a necessidade de um maior fator de qualidade (LEE, 2004; RAZAVI, 2012). Já para um IF menor o processo de rejeição de interferências na banda desejada é facilitado (LEE, 2004; RAZAVI, 2012). Em suma: valor de  $\omega_{IF}$  alto: melhor rejeição de imagem e pior seletividade. Valor  $\omega_{IF}$  baixo: melhor seletividade e pior rejeição de imagem.

Esse *trade-off* pode ser resolvido utilizando uma arquitetura com dois misturadores, cada um seguidos por um estágio de amplificação e filtragem (RAZAVI, 2012). A partir dessas análises, outras arquiteturas alternativas foram desenvolvidas como os receptores rejeita imagem e receptores com baixo IF (RAZAVI, 2012; LEE, 2004).

Um outro processo para recepção de sinais, consiste em converter diretamente o sinal de RF para o sinal banda base. Para esse processo tem-se os receptores homodino, também chamados de receptores de conversão direta ou zero IF. De acordo com Razavi (2012) algumas características mais atrativas dos receptores homodinos em comparação com o heteródino são: ausência da frequência imagem e seleção de canal realizada por um filtro passa-baixas. Embora possam sofrer com maiores quantidades de ruido, essas características tornam esse tipo de receptor mais simples e com maior integração, uma vez que filtros passa-baixas são mais fáceis de serem projetados dentro de um chip (RAZAVI, 2012). Além disso, essas arquiteturas não necessitam de osciladores, misturadores ou filtros de RF e por esse motivo são soluções com menor custo (ADVANTAGES..., c2012a). Ao longo desse capítulo uma arquitetura de receptor de conversão direta será discutida, mostrando também ser uma escolha interessante para aplicações de baixo consumo.

No que se refere a métrica da sensibilidade as arquiteturas do tipo heteródina historicamente apresentam uma melhor performance em comparação com as arquiteturas homódinas (ADVANTAGES..., c2012b). No entanto, técnicas para melhoria da sensibilidade em arquiteturas homódinas vem sendo exploradas na literatura. No trabalho apresentado em Cheng e Chen (2017) os autores apresentam uma topologia para o casamento de impedância com o intuito de melhorar a sensibilidade de um conversor de detecção direta, com detector de RF ativo. Em Wentzloff et al. (2021) os autores trazem uma revisão a respeito das métricas dos receptores e a importância de soluções com baixo consumo e bom desempenho nos sistemas de comunicação sem fio para IOT, abordando sobre o uso de detectores do tipo passivo.

# 2.2 Receptores de Baixo Consumo

Uma técnica aplicada no projeto de receptores de baixo consumo é utilizar arquiteturas de receptores onde o primeiro estágio consiste em um bloco detector (MOODY et al., 2019; YAN et al., 2018). Essa abordagem, conhecida como arquitetura de conversão direta ou detecção direta de RF, elimina a necessidade de blocos de amplificação de baixo ruido (do inglês, *Low-Noise Amplifier* - LNA) e osciladores locais (LO, do inglês *Local Oscilator*) de RF para a operação de *down conversion* (CHENG; CHEN, 2017; WENTZLOFF et al., 2021).

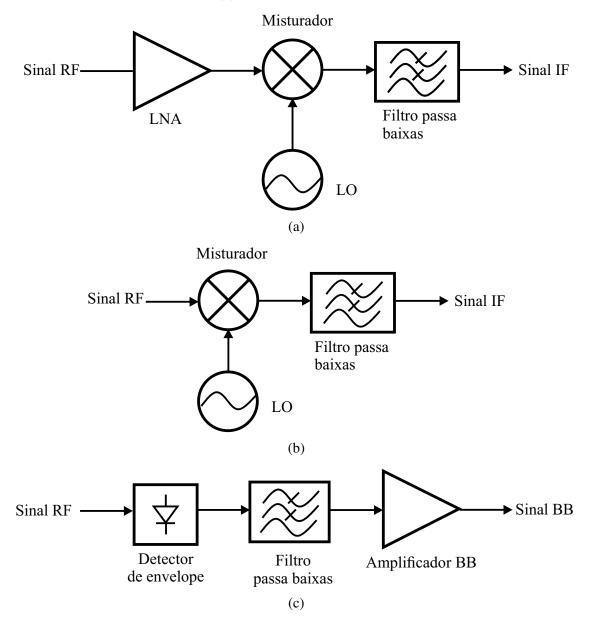

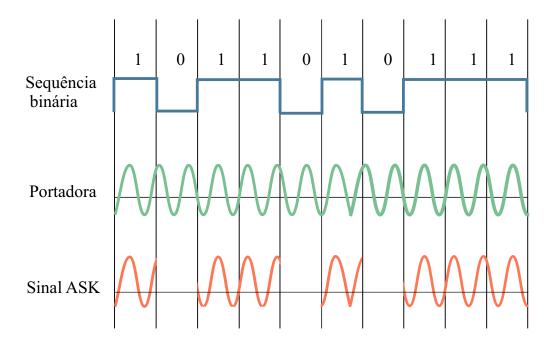

A Figura 3a apresenta o diagrama de blocos de um receptor com LNA no primeiro bloco e a Figura 3b ilustra uma arquitetura com misturador no primeiro estágio, ambas as arquiteturas de receptor são do tipo heteródino. Esses blocos de LO e LNA adicionam a necessidade de um maior consumo de energia (MOODY et al., 2019; WENTZLOFF et al., 2021). A Figura 3c mostra o diagrama de blocos de uma topologia do tipo homódina com detector de envelope no

primeiro estágio.

Figura 3 – Arquitetura de receptores: (a) LNA na entrada para melhor performance de ruído; (b) misturador na entrada e (c) conversão direta.

Fonte: Autora (2023).

No caso das arquiteturas de conversão direta, o bloco de detecção de envelope, que consiste no primeiro estágio do receptor, faz a conversão do sinal de RF para sinal banda base, ou seja, realiza a etapa de *down conversion*. A Figura 4 exibe um comparativo entre as arquiteturas de receptores encontradas na literatura apresentado em Moody et al. (2019). Nela é mostrada a relação entre sensibilidade e consumo de energia para receptores de conversão direta e outras arquiteturas. Observando a imagem, é possível inferir que baixo consumo de energia pode ser obtido em receptores com detecção direta, mas em alguns casos a sensibilidade é comprometida.

Figura 4 – Comparativo entre receptores encontrados na literatura.

Fonte: Adaptado de Moody et al. (2019).

No que se refere ao circuito detector de envelope, existem dois tipos, os detectores ativos e os detectores passivos. De acordo com Moody et al. (2019), a escolha do tipo de detector deve ser avaliada a partir de duas métricas: consumo de energia e sensibilidade. No entanto, ambas as classes de detectores possuem sensibilidade limitada pelo ruido produzido e falta de ganho do *front-end* de RF (MOODY et al., 2019). Com relação ao consumo de energia, os detectores de envelope passivos são mais eficientes em aplicações com taxa de dados menores do que 1*KB/s* (MOODY et al., 2019).

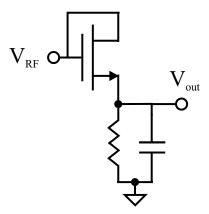

O detector em sua forma mais simples consiste em um diodo conectado a um capacitor e funciona como um retificador. Quando o sinal de entrada é maior do que o sinal na saída mais a queda de tensão do diodo, o diodo conduz e o capacitor é carregado com uma tensão que "persegue"a tensão de entrada (PARK; WILSON; ISMAIL, 2006). Uma adaptação para obter o comportamento do diodo e implementa-lo em processo CMOS é utilizar um transistor conectado como diodo, como mostra a Figura 5.

Figura 5 – Detector de envoltória com Mosfet conectado como diodo.

Fonte: Autora (2023).

A topologia de Mosfet conectado como diodo consiste em um detector do tipo passivo e analogamente ao comportamento do diodo, essa configuração retifica o sinal de RF e o filtro na saída filtra as componentes de baixas frequências (CHENG; CHEN, 2017). Observando a conexão dessa topologia, é possível inferir que uma limitação dela é a necessidade do sinal de entrada ser maior do que a tensão de *threshold* (limiar) do transistor.

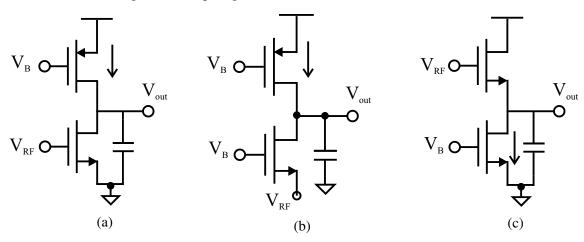

Além dessa topologia, as arquiteturas convencionais de detectores podem ser dividas em três tipos: fonte comum (CS, do inglês *common source*), porta comum (CG, do inglês *common gate*) e dreno comum (CD, do inglês *commom drain*) (OU; FERREIRA, 2018; YAN et al., 2018). A topologia CS pode ainda ser subdividida em: polarização com fonte de corrente (ilustrada na Figura 6a) e auto polarizada (SB-CS, do inglês *self-biasing*), quando possui um resistor de realimentação. A Figura 6 mostra a conexão dessas topologias.

Figura 6 – Topologia de detectores: (a) CS; (b) CG e (c) CD.

As topologias de detectores mostradas são do tipo ativo. Os autores em Cheng e Chen (2017) examinaram as principais características dessas topologias e demonstraram que a topologia

Fonte: Autora (2023).

com fonte comum apresentou um melhor ganho de conversão em comparação com as outras. Os autores se aprofundaram nessa topologia e obtiveram uma sensibilidade de -50~dBm com um consumo de  $2,4~\mu W$  em tecnologia CMOS de 180~nm. Para atingir esse resultado eles utilizaram uma técnica para melhorar o ganho de conversão utilizando um pseudo resistor de realimentação para aumentar a resistência na saída. De acordo com Ou e Ferreira (2018) essa é uma das técnicas encontradas na literatura para melhorar o ganho de conversão, a outra seria utilizar uma rede de casamento na entrada do detector.

Em Ou e Ferreira (2018) os autores apontam uma topologia do tipo CS, onde o ganho de conversão é melhorado utilizando um indutor ativo. Para a tecnologia CMOS de 130 nm, foi obtida uma sensibilidade de -60~dBm com um consumo de energia de  $2,4~\mu W$ . O trabalho descrito em (YAN et al., 2018) demonstra um receptor com um detector CS e uma rede de casamento LC com alto fator de qualidade, obtendo assim uma sensibilidade de -58~dBm para o consumo de 1  $\mu W$  com tecnologia de 95 nm.

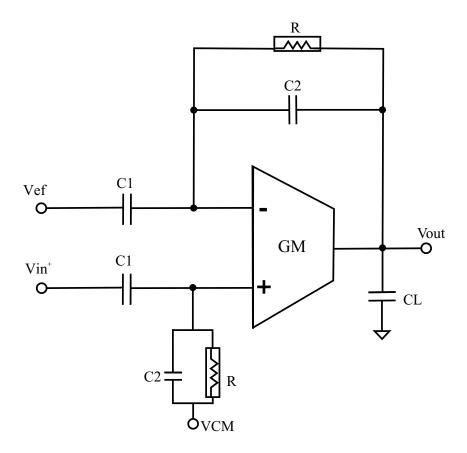

Em relação aos detectores passivos, estes podem adicionar uma grande quantidade de ruido ao circuito em virtude da quantidade de harmônicos e nível DC, por esse motivo, um estágio de filtragem e, posteriormente amplificação banda base, são necessários (WENTZLOFF et al., 2021). Uma arquitetura de amplificador com bom desempenho em varias aplicações é o amplificador com acoplamento CA (HARRISON; CHARLES, 2003; VIANA; BELFORT, 2019; ZHANG et al., 2018). A Figura 7 ilustra a configuração do amplificador com acoplamento CA.

Vin Cl GM Vout

Vin Cl CL R

Figura 7 – Arquitetura de amplificador com acoplamento AC.

Fonte: Autora (2023).

De acordo com Harrison e Charles (2003) essa arquitetura é atraente para amplificação de sinais banda base em receptores de conversão direta, pois nesse tipo de aplicação, pode existir grandes níveis de *offsets*, decorrentes da incompatibilidade dos dispositivos e acoplamento do substrato, contudo, essa arquitetura de amplificador, fornece um bom nível de rejeição de *offsets*/níveis DC e ruídos de baixa frequência (ruído *flicker*) na entrada, enquanto alcançam um bom desempenho AC em frequências ultra-baixas.

Como circuito interno ao amplificador foram avaliadas na literatura referências sobre amplificadores de transcondutância (OTA, do inglês, *Operational Transconductance Amplifier*). As topologias mais encontradas na literatura de OTA são: Miller, *cascode telescopic*, *Folded-Cascode* e *Current-Mirror* (VIANA; BELFORT, 2019; VIANA, 2019; JUSOH; RUSLAN, 2020). O OTA Miller possui um maior consumo de energia em comparação com as outras topologias, além da necessidade de um método de compensação para estabilização da resposta em frequência, o *Cascode telescopic* embora possua um melhor consumo em comparação com o OTA Miller, possui uma menor variação na saída quando comparado com as demais arquiteturas (JUSOH; RUSLAN, 2020; OLIVEIRA; BRITO-FILHO, 2022).

Em Viana e Belfort (2019), Viana (2019) as arquiteturas *folded-cascode* e *current-mirror* foram avaliadas. A Figura 8a exibe o esquemático de uma topologia padrão *folded-cascode* (WATTANAPANITCH; FEE; SARPESHKAR, 2007) e a Figura 8b ilustra a arquitetura *current-mirror* apresentado em Viana e Belfort (2019), Viana (2019).

M9  $M_{c1}$ VcasS Ibias M7 M8 VcascP 🔿 V<sup>+</sup>**о**Д м1 O Vout M2M5 Vbias -M6 M3 M4  $M_{c3}$ (a) **Q** VDD M7 M8 M10 V<sub>out</sub> M1 Vino **-O**Vin<sup>+</sup> M5 M6 M3 VSS 6 (b)

Figura 8 – Arquitetura de OTA: (a) *folded-cascode* e (b) *current-mirror*.

Fonte: Autora (2023).

A topologia *folded-cascod* convencional pode adicionar muito ruído em virtude da elevadas correntes de canal formada pelo espelho de corrente dos transistores M3 e M4 (WAT-TANAPANITCH; FEE; SARPESHKAR, 2007). A topologia *current-mirror* é uma configuração

mais simples em comparação com as outras topologias. De acordo com o comparativo realizado em Viana (2019), Viana e Belfort (2019), o OTA *current-mirror* apresentou um menor consumo de energia, sendo obtido um consumo de 1,5  $\mu$  W, em processo CMOS de 0,5  $\mu$ m. Além disso, o OTA *current-mirror* mostrou-se melhor em termos de ganho e Razão de Rejeição de Modo Comum (CMRR, do inglês, *Common Mode Rejection Ratio*), quando comparado a arquitetura textitfolded-Cascode que foi discutida pelos autores.

Fazendo a ponte entre o sinal analógico e o ASIC digital, um conversor analógico-digital (ADC, do inglês *Analog-to-digital converter*) é necessário. Nessa aplicação o objetivo desse estágio é entregar um nível de amplitude constante ao processamento digital, digitalizando o sinal banda-base da saída do amplificador. Um circuito comparador exerce essa função, criando uma interface entre o sinal analógico e o sinal digital.

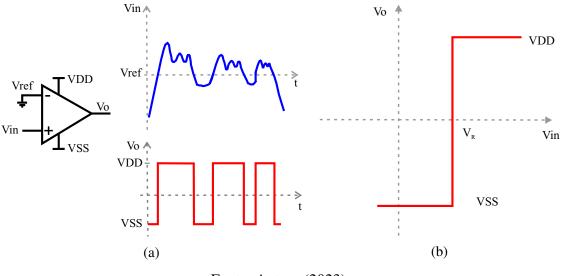

De modo geral os comparadores podem ser divididos em comparadores sem histerese e comparadores com histerese. A Figura 9a ilustra o principio de funcionamento de um comparador sem histerese e sua função de transferência é ilustrada na Figura 9b.

Figura 9 – Funcionamento de um comparador sem histerese: (a) sinais de entrada e saída; (b) função de transferência.

Fonte: Autora (2023).

Avaliando a Figura 9 é possível inferir que o comparador, como o próprio nome sugere, faz a comparação entre dois sinais na entrada e com base nesses sinais, a saída será um nível alto ou nível baixo. Essa comparação pode ser feita em sinais de tensão ou corrente e o sinal digital na saída representa se o sinal de entrada é maior ou menor do que o sinal de referência (BOYLESTAD; NASHELSKY, 2013). Contudo, considerando um sinal de comunicação mais realístico, com ruído e oscilações próximas a tensão de referência, o funcionamento desse comparador seria instável, como demonstrado na Figura 9a. Uma solução para esses casos é utilizar um comparador com histerese. A Figura 10 ilustra o principio de funcionamento e a

função de transferência de um comparador com histerese.

Figura 10 – Principio de funcionamento de um comparador com histerese: (a) sinais de entrada e saída; (b) função de transferência.

Fonte: Autora (2023).

O comparador com histerese possui dois níveis de tensões de limiar (GOWDA; KAMAT, 2020). O conceito de histerese nesses casos representa a diferença entre a tensão de limiar superior  $(V_{TH})$  e inferior  $(V_{TL})$  (SEDRA; SMITH, 2015). Os comparadores possuem dois estados estáveis e permanecem em um estado até que uma ação, ou *trigger*, faça a comutação para o outro estado, além disso, na região de histerese o nível da saída depende do estado em que a saída já estava (SEDRA; SMITH, 2015). A tensão de entrada funciona como o *trigger*.

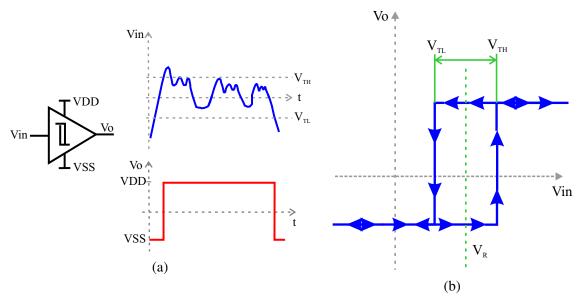

O bloco seguinte do receptor de conversão direta, consiste em uma etapa para eliminar falsas detecções, por meio de correlacionadores que devem identificar ativações e desativações do sinal (WENTZLOFF et al., 2021). Essa etapa pode ser realizada por meio da técnica de chaveamento *ON-OFF Keying* (OOK). Consoante a Cheng e Chen (2017), o uso da técnica OOK, é geralmente empregado em sistemas que objetivam redução de consumo e complexidade. Essa técnica OOK aplicada na modulação ASK (*Amplitude Shift Keying*) permite modular o sinal por meio de alterações na amplitude da portadora. Considerando o sistema binário, tem-se dois níveis de amplitude, uma para representação do bit '0' e outro para representação do bit '1'. Para o bit '1' o sinal modulado consiste no sinal da portadora, para o bit '0' o sinal modulado possuirá uma amplitude 0 ou algum outro nível fixo. Desse modo, tem-se o sinal ilustrado na Figura 11. A demodulação, faz o processo de converter o sinal recebido dos estágios anteriores em *bitstream*, recuperando assim o sinal da informação.

Figura 11 – Ilustração do Funcionamento da Modulação Digital ASK.

Fonte: Autora (2023).

### 2.3 Sensibilidade

Uma métrica importante na análise de receptores é o mínimo sinal detectável, ou seja, a sensibilidade. A sensibilidade representa o nível mínimo de sinal necessário para atingir uma uma taxa de erro de bit, geralmente de  $10^{-3}$  (WENTZLOFF et al., 2021). Alguns parâmetros dos receptores limitam a sensibilidade, a saber, ganho do *front-end* de RF, tipo do receptor, ruido adicionado, largura de banda, potência e taxa de dados (WENTZLOFF et al., 2021; CHENG; CHEN, 2017). A definição da sensibilidade é matematicamente expressa pela equação (2.2).

$$PSen = NF + 10 \times \log(BW) - 174 \, dBm/Hz + SNR_{Min} \tag{2.2}$$

Para determinação da sensibilidade também é necessário encontrar a figura de ruído. Essencialmente, a figura de ruído é a relação do SNR da entrada pelo SNR da saída, as outras

expressões são derivadas dessa definição. A figura de ruído do detector pode ser determinada a partir da equação (2.3) (CHENG; CHEN, 2017).

$$NF = 1 + \frac{No}{N_s C_G^2} \tag{2.3}$$

Em que, No é o ruído total na saída em  $V^2/Hz$ , Ns o ruído devido a resistência da fonte de entrada e  $C_G$  é o ganho de conversão. A figura de ruído pode ser calculada com relação a entrada ou a saída.

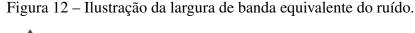

No cálculo do ruido para determinação da sensibilidade deve-se levar em consideração a largura de banda equivalente do ruído. Nesse trabalho, essa definição foi avaliada, uma vez que foi aplicada no trabalho de (CHENG; CHEN, 2017) para cálculo da sensibilidade do detector ativo. Em geral, a largura de banda do ruído não é a mesma largura da frequência em  $-3 \, dB$ , a largura de banda efetiva do ruído é definida como uma filtro com resposta perfeitamente retangular que possui a mesma quantidade de potência de ruído integrado que o filtro real (CHENG; CHEN, 2017; LEE, 2004; SOLUTIONS, c2023; SOBERING, 1991). Devido a essa resposta perfeitamente retangular esse comportamento também é chamado de *brick wall* (termo do inglês para parede de tijolos). A Figura 12 ilustra essa definição.

A Figura 12 é meramente ilustrativa para facilitar o entendimento do conceito. A largura de banda equivalente do ruído (ENBW, do inglês *Equivalent Noise Bandwidth*) é maior que a largura de banda do filtro com frequência de corte em  $-3 dB (f_{3dB})$ . Para determinar essa o valor

do ENBW, um fator de correção, também chamado de fator de *brick wall* é aplicado. A equação (2.4) contempla esse conceito.

$$ENBW = fc_{3dB} \times K_n \tag{2.4}$$

Sendo  $K_n$  o fator de correção e depende da ordem do filtro. Considerando um filtro RC de primeira ordem, a largura de banda do ruído é:  $\pi/2 \times f_{-3dB}$ , resultado que tem coerência, tendo em vista que um filtro RC simples possui componentes de ruído além da frequência de corte (LEE, 2004; SOLUTIONS, c2023; SOBERING, 1991). Em Cheng e Chen (2017), os autores utilizaram essa relação para cálculo da potência do ruído integrado do detector.

O ruído total na saída pode ser determinado integrando a densidade espectral de potência (PSD, do inglês *power spectral density*) ao longo da faixa de frequência. O resultado é dado em unidade de  $Volts^2$  ( $V^2$ ) (WILLIAMS, 2015). Matematicamente, isso pode ser escrito como na equação (2.5).

$$PN = \int_{f_t}^{f_H} (V_e)^2 df \ V^2 \tag{2.5}$$

PN é a potência do ruído, $V_e$  é a tensão do ruído da densidade espectral. Para encontrar o valor RMS do ruído, deve-se calcular a raiz quadrada. Resultando em um valor em unidade de Volts RMS (equação 2.6)).

$$VN = \sqrt{PR} \ (V_{RMS}) \tag{2.6}$$

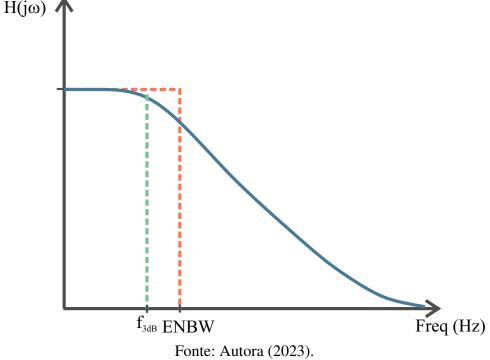

Outro conceito necessário na determinação da figura de ruido para cálculo da sensibilidade é a analise de ruido em cascata. A Figura 13 ilustra um sistema em cascata e a equação (2.7) mostra como calcular o fator de ruido total em um sistema com múltiplos estágios.

Figura 13 – Blocos em cascata.

Fonte: Autora (2023).

Analisando o sistema da Figura 13 com N estágios, o fator de ruído total será dado pela equação (2.7).

$$f_{total} = f1 + \frac{f2 - 1}{g1} + \frac{f3 - 1}{g1g2} + \dots + \frac{fN - 1}{g1g2g3 \dots g_{N-1}}$$

(2.7)

Os valores de f e g são dados em escala linear. Para obter a figura de ruído basta calcular o valor em decibel do fator de ruído total, encontrado com a equação (2.7). Logo,

$$NF = 10 \times \log(f_{total}) \tag{2.8}$$

.

# 2.4 Resumo do capítulo

Este capítulo trouxe uma revisão bibliográfica a respeito das arquiteturas de receptores, mostrando vantagens e limitações dos receptores heteródinos e homodinos. Como discutido ao longo do capitulo, as arquiteturas homodinas são conhecidas pela simplicidade, baixo custo, menor consumo de energia e menor sensibilidade quando comparadas com os receptores heteródinos. Nesse contexto, uma arquitetura de conversão direta foi apresentada, em virtude da proposta desse trabalho em avaliar o *trade-off* entre consumo de energia e uma técnica para melhoria da sensibilidade.

As arquiteturas convencionais de detectores de envoltória foram abordadas e a topologia do amplificador com acoplamento capacitivo foi introduzida. Por fim, as expressões para determinação da sensibilidade foram apresentadas, sendo possível inferir que as principais métricas para a análise da sensibilidade são: ruído (presente na equação como figura de ruído) e seletividade (largura de banda do canal).

O capítulo 3 exibirá os circuitos da arquitetura proposta, apresentando seus esquemáticos, além da metodologia e fluxos de projetos aplicados no desenvolvimento desse trabalho e finaliza com o *setup* de teste dos ASICs.

#### 3 SISTEMA PROPOSTO E METODOLOGIA

Este capítulo descreverá o sistema proposto, a metodologia aplicada e as ferramentas que serão empregadas no projeto do receptor. Para testar a hipótese sobre a técnica para melhoria da sensibilidade, bem como a arquitetura do receptor, as tecnologias CMOS *SkyWater* 130 nm e UMC 180 nm serão utilizadas. A modelagem dos circuitos do receptor será realizada com os modelos dessas tecnologias e as ferramentas EDA de cada fluxo serão utilizadas para simulações, *layout* e prototipagem dos ASICs.

Na primeira seção deste capítulo, os circuitos propostos para cada bloco do receptor serão mostrados. Posteriormente, a seção 3.2 exibirá as etapas da elaboração da pesquisa, o fluxo de projeto *open-source* da *SkyWater* 130 nm para projeto de um ASIC do tipo analógico e digital, além do fluxo para projeto com a tecnologia UMC 180 nm. A seção final do capítulo ilustrará o *setup* para testes experimentais do *chip*.

# 3.1 Sistema Proposto

Essa seção irá discorrer sobre os circuitos examinados e avaliados em tecnologia CMOS. Será apresentado desde o esquemático do detector até o demodulador ASK OOK. A Figura 14 ilustra o diagrama do sistema proposto, constituído por um detector de envelope, um amplificador banda base, conversor analógico para digital e um MODEM ASK. Os blocos em cinza, representam o *front-end* do transmissor e não são o foco desse trabalho, são apenas para ilustração completa do transceptor.

MODEM

Bitstream

Amplificador banda base

Conversor AD

FPGA

ASIC

TXout

Rede de Casamento

Figura 14 – Diagrama de blocos do sistema proposto.

Fonte: Autora (2023).

O diagrama de blocos da Figura 14 expõe os estágios que compõem o receptor de conversão direta. O detector de envoltória, bem como o amplificador com acoplamento CA integram o ASIC analógico, os blocos digitais serão implementados e testados com o FPGA e o comparador fará a ponte entre essas tecnologias.

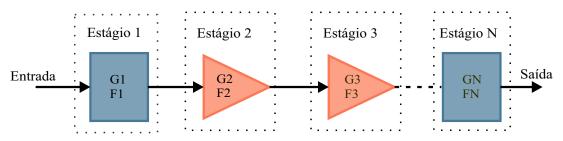

Considerando as observações levantados no capítulo 2 e a proposta em utilizar uma topologia de detecção passiva para quantificar a sensibilidade, como base em Wentzloff et al. (2021), bem como validar o uso do amplificador com acoplamento CA em receptores de conversão direta, como sugere Harrison e Charles (2003), o detector de envelope analisado nesse trabalho é ilustrado na Figura 15.

Cin

Figura 15 – Esquemático do detector de Envelope.

Fonte: Autora (2023).

A topologia da Figura 15 foi inicialmente proposta por Piovani e Sousa (2011). O detector é composto por um transistor MOSFET tipo N, um capacitor de acoplamento no terminal dreno e um filtro RC na saída. No trabalho, os autores apresentam uma análise quase-estática do detector, com o MOSFET operando na região de tríodo. Para a configuração mostrada na Figura 15, os autores demonstraram que a tensão de dreno é sempre positiva, considerando que não há fluxo de corrente DC no transistor, o transistor satura em inversão fraca e a tensão na saída não depende das dimensões do transistor (PIOVANI; SOUSA, 2011).

Na presença de um sinal RF na entrada, isto é, entre o dreno e a fonte, um fluxo de corrente rico em harmônicas, segue pelo canal do dispositivo (PIOVANI; SOUSA, 2011). Na saída, um filtro RC faz a seleção das frequências abaixo da frequência de corte (Equação (3.1)) e o capacitor na entrada proporciona uma alta impedância para as componentes com níveis DC.

$$f_c = \frac{1}{2\pi RC} \tag{3.1}$$

Além da análise transiente e a verificação do ruído, o ganho de conversão, dado pela equação (3.2), será utilizado para avaliar a performance do detector.

$$CG = 20\log\left(\frac{Vout_{RMS}}{Vin_{RMS}}\right). \tag{3.2}$$

A equação (3.2) determina o ganho de tensão, sendo  $Vout_{RMS}$  o valor da tensão RMS na frequência da saída e  $Vin_{RMS}$  a tensão RMS na entrada.

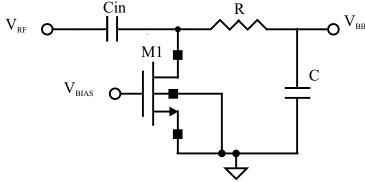

A escolha da arquitetura do amplificador banda base, foi fundamentada na pesquisa de Harrison e Charles (2003). No trabalho os autores analisaram o desempenho da arquitetura como amplificador de biosinal, sendo uma opção para aplicações de baixo consumo e baixo ruido. Tendo em vista que os receptores integrados de conversão-direta são atrativos para aplicações de baixo consumo, mas sofrem com a presença de ruído em baixas frequências, essa arquitetura de amplificador com capacitores de acoplamento nas entradas, resulta em uma redução desses níveis DC/offsets e ruídos de baixa frequência (ruído flicker) na entrada (HARRISON; CHARLES, 2003; VIANA, 2019). Com a finalidade de trazer mais portabilidade ao circuito, optou-se por utilizar o amplificador na configuração não-inversora com fonte simples. A Figura 16 mostra a configuração do amplificador com acoplamento AC utilizada nesse trabalho (KASSIRI; ABDELHALIM; GENOV, 2013).

Figura 16 – Configuração do amplificador com acoplamento AC com fonte simples.

Fonte: Autora (2023).

Considerando que a resistência (R) possui um valor muito grande, o ganho de banda média do amplificador com acoplamento CA é definido pela relação entre os capacitores de

acordo com a Equação (3.3) (HARRISON; CHARLES, 2003).

$$A_M = \frac{C_1}{C_2} \tag{3.3}$$

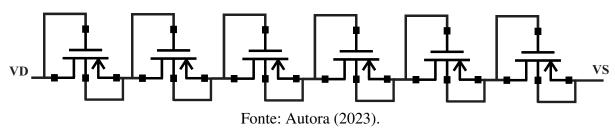

Para obter altos valores de resistência, pode-se empregar o uso de transistores, obtendo assim, um pseudo-resistor. Com o uso de pseudo-resistores, é possível obter resistências com valores elevados (na ordem de  $10^{10}~\Omega$ ) em uma área pequena, se comparado com os resistores de polisilício. Essa característica é atrativa e essencial no desenvolvimento de circuitos integrados. A Figura 17 ilustra a conexão dos transistores do pseudo resistor. Essa configuração foi avaliada em (VIANA, 2019) com o melhor compromisso entre resistência e boa linearidade.

Figura 17 – Arquitetura do pseudo resistor.

A largura de banda para o amplificador com acoplamento AC, é definida pela Equação (3.4), considerando que o  $C_1, C_L >> C_2$  (HARRISON; CHARLES, 2003).

$$BW = \frac{GM}{A_M C_L} \tag{3.4}$$

Sendo  $G_M$  a trânscondutância do amplificador OTA,  $A_M$  é o ganho na banda média e  $C_L$  é o capacitor de carga. A frequência de corte inferior é definida na Equação (3.5) e a frequência de corte superior em Equação (3.6) (HARRISON; CHARLES, 2003; ZHANG et al., 2018).

$$f_L = \frac{1}{2\pi RC_2} \tag{3.5}$$

$$f_H = \frac{GM}{2\pi A_M C_L} \tag{3.6}$$

Além de avaliar o amplificador por meio das simulação de ganho e transiente, também serão analisados o *Noise Efficiency Factor* (NEF) (equação (3.7)), *Total Harmonic Distortion* (THD) (Equação (3.8)) e a Razão de Rejeição de Modo Comum (do inglês, *Common Mode Rejection Ratio* - CMRR).

$$NEF = V_{re,RMS} \times \sqrt{\frac{2I_{tot}}{\pi V_t 4kTBW}}$$

(3.7)

Em que,  $V_{re,RMS}$  é a tensão do ruído referenciado na entrada,  $I_{tot}$  é a corrente total,  $V_t$  é a tensão térmica, K é a constante de Boltzmann, T é a temperatura em Kelvin e BW é a largura de banda do ruído.

$$THD = \frac{1}{Vl} \sqrt{\sum_{i=2,3}^{\infty} V_n^2}$$

(3.8)

Em que,  $V_l$  é o valor da componente fundamental e  $V_n$  é valor da n-ésima componente harmônica.

Aprofundando no circuito do amplificador, foram avaliadas as arquiteturas de amplificadores operacionais de transcondutância como núcleo do amplificador com acoplamento capacitivo. Com base nas consideração discutidas no capítulo 2 o OTA espelho de corrente será utilizado (esquemático ilustrado na Figura 8b).

A proposta para fazer a ponte entre os sinais analógicos e digitais é utilizar um circuito comparador *Schmitt trigger*. A Figura 18 ilustra essa conexão. Os resistores são utilizados para definir os níveis de histerese.

CI externo

Figura 18 – Conexão entre o comparador e o FPGA.

Fonte: Autora(2023).

Além dos blocos já apresentados, uma rede de casamento entre a antena e a entrada do receptor é necessária. Esse primeiro estágio garante a máxima transferência de potência, reduz a reflexão na entrada do receptor e é uma das técnicas utilizadas para aumentar o ganho de conversão (OU; FERREIRA, 2018). Para garantir a máxima transferência de potência, uma rede LC simples será utilizada.

#### 3.2 Metodologia

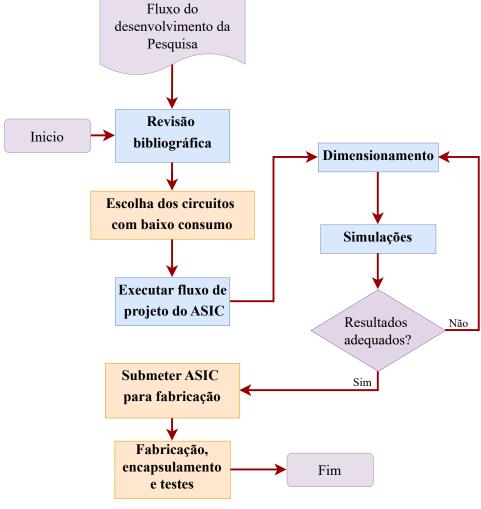

A realização dessa pesquisa pode ser dividida em etapas, sendo estas especificadas na Figura 19.

Figura 19 – Etapas para a realização da pesquisa.

A primeira etapa da pesquisa consistiu em um levantamento bibliográfico a respeito dos sistemas de recepção, fundamentos da microeletrônica, projeto de circuitos integrados, blocos e aplicações de receptores de baixo consumo. Após essa etapa é realizada a modelagem em nível de sistema. Nessa fase, foram avaliados todos os estágios necessários para composição do receptor de baixo consumo. Após essa análise, os subsistemas foram implementados. Para isso, foram utilizadas modelos e ferramentas das tecnologias CMOS para projeto de um *ASIC*.

Seguindo com a etapa de dimensionamento, são realizadas simulações no domínio do tempo e da frequência para verificar o funcionamento de cada circuito. Com o funcionamento adequado de cada bloco, o ASIC pode ser prototipado e submetido para fabricação. Como etapa final, trabalhos são escritos com o intuito de contribuir com o estado da arte sobre os receptores de baixo consumo. As subseções seguintes detalham o fluxo de projeto do ASIC para cada uma das tecnologias aplicadas nessa pesquisa.

## 3.2.1 Fluxo de Projeto *Open-source*

Para prototipagem com a tecnologia *SkyWater* 130 nm será utilizado o fluxo de projeto com ferramentas e tecnologia do tipo *open-source*. A *SkyWater* em parceria com a *Efabless* e Google disponibilizou, desde 2020, um *Process Design-Kit* (PDK) para projeto e manufatura de circuitos integrados para testes e verificação inicial. Esse *open* PDK proporciona uma grande oportunidade para aprendizagem do processo de projeto e concepção de um circuito integrado, e por esse motivo foi utilizado nessa pesquisa. Além do PDK, serão utilizadas ferramentas livres já bastantes consolidadas no desenvolvimento de circuitos integrados. A Figura 20 resume o fluxo de projeto de um ASIC do tipo analógico e as ferramentas livres utilizadas em cada etapa. Esse fluxo é aplicável no desenvolvimento do detector de envelope, assim como do amplificador implementados com a tecnologia CMOS *SkyWater* 130 nm.

Fluxo de projeto do ASIC analógico Magic Layout Plataforma *Efabless* Gerar arquivo Precheck Inicio **GDS** Plataforma Efabless gm/Id Netgen Scripts em Python LVS Tape-out Sizing Sim Fabricação, Xschem Não encapsulamento Resultados adequados? e testes Captura de esquemático Fim Ngspice Ngspice Simulações Simulações pré-layout pós-layout Magic Layout Não Sim Resultados Layout, DRC e adequados? extração de parasitas

Figura 20 – Fluxo de projeto de um ASIC analógico e as ferramentas em cada fase.

Fonte: Autora (2023).

geraram as informações necessárias para o projeto foram implementados com a linguagem de programação *Python* 3 (o algoritmo utilizado pode ser encontrado na referência Tclarke (2020)). A respeito das ferramentas indicadas na Figura 20, o *XSCHEM*, consiste em um *front-end* para a captura de esquemáticos e funciona com o *NGSPICE* no *back-end*. Os esquemáticos criados no *XSCHEM* geram *netlists*, que são simulados com auxílio do *NGSPICE*.

Na etapa de verificação, o *MAGIC Layout* e *NETGEN* auxiliam na análise DRC (do inglês, *Design Rule Check*) e LVS (do inglês, *Layout Versus Schematic*), respectivamente. As etapas de *precheck*, *tape-out* são realizadas na plataforma da *Efabless*, por fim, a fabricação é realizada com o programa *Open MPW* disponibilizado pela parceria entre *Google*, a *foundry SkyWater* e a *Efabless* (*EFABLESS CORPORATION*, c2022).

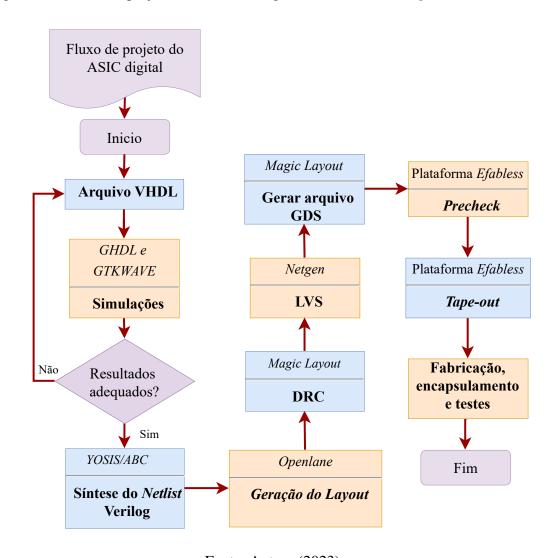

A Figura 21 expõe uma visão geral das etapas de desenvolvimento de um ASIC digital.

Figura 21 – Fluxo de projeto de um ASIC digital e as ferramentas open-source utilizadas.

Fonte: Autora (2023).

Diferente do fluxo analógico, o fluxo digital é feito majoritariamente de forma automática.

A primeira etapa consiste no desenvolvimento dos algoritmos em linguagem de descrição de hardware. Posteriormente os arquivos de teste são criados e realizadas as simulações, utilizando GHDL e GTKWAVE. A ferramentas YOSIS é utilizada para o arquivo Verilog a partir do arquivo VHDL implementado. Essa etapa de conversão de VHDL e Verilog é dispensável quando os algoritmos são implementados diretamente em Verilog. A etapa seguinte consiste na síntese RTL (Register Tranfer Level) que inicia as etapas de síntese física do circuito em nível de registradores. O arquivo Verilog é a entrada da ferramenta Openlane. A ferramentas Openlane integra scripts que rodam outras ferramentas com o objetivo de gerar um layout otimizado, entregando na saída, o arquivo final da fabricação (GDSII).

Uma solução para o desenvolvimento de *hardware* com alto grau de paralelismo e reconfigurabilidade é alcançada com o FPGA. Em comparação com o ASIC, os FPGAs possuem uma área maior e consomem mais energia (AKEELA; DEZFOULI, 2018). No entanto a característica de reconfigurabilidade torna o FPGA uma alternativa promissora nos projetos de módulos digitais. De modo geral, é possível desenvolver o projeto, configura-lo no FPGA e realizar a validação experimental, com possibilidade de eventuais ajustes e alterações.

Com essas caraterísticas o FPGA pode ser usado para validar o projeto e assim, posteriormente, realizar a confecção do ASIC. Isso é viável devido as semelhanças entre o fluxo de projeto de ambas as tecnologias. O fluxo de projeto com o ASIC e o FPGA possui um *front-end* em comum, diferindo apenas no *back-end*, ou seja, nas etapas de *layout* e finalização do *chip*, uma vez que o ASIC é fabricado de forma customizada para o projeto e os FPGAs possuem células programáveis.

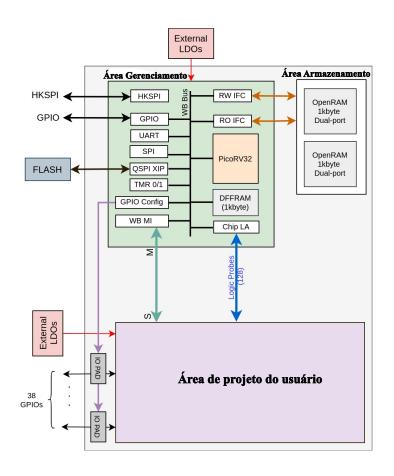

Outra inovação incorporada com o fluxo *open-source* é o fornecimento de uma área pré-caracterizada para integração do chip desenvolvido. Essa área possui um espaço de 10 mm² para o projeto do usuário, além de uma área de gerenciamento e uma área de armazenamento, sendo disponibilizada para projetos analógicos e digitais (*EFABLESS CORPORATION*, 2020). A Figura 22 mostra o diagrama de blocos da *harness caravel*, ilustrando as áreas de projeto do usuário, gerenciamento e armazenamento.

Figura 22 – Harness Caravel.

Fonte: Adaptado de Efabless corporation (2020).

Esse modelo de SoC pré-caracterizado é nomeado como *harness caravel* para um ASIC digital e *harness caravan* para ASIC analógico. De modo geral a principal diferença entre as duas *harness*, consiste em uma alteração em alguns GPIOs para sinais de alta velocidade, alta tensão e sensíveis ao ruído. A Figura 23 ilustra o processo de integração entre o projeto de usuário e o SoC fornecido pelo textitopen MPW.

Projeto do usuário

Caravel

Chip Integrado

Figura 23 – Ilustração da integração com a*Harness*.

Fonte: Adaptado de Efabless corporation (c2022).

Após a fabricação, o *chip* é enviado com a PCB conectada aos pinos utilizados da *harness*.

# 3.2.2 Fluxo de Projeto com ferramentas da Cadence

A Figura 24 mostra o diagrama de blocos do fluxo de projeto, bem como as ferramentas utilizadas.

Fluxo de projeto do ASIC analógico Tape-out Inicio Fabricação, encapsulamento gm/Id e testes Arquivo Scripts em Python **GDS** Sizing Fim Sim Cadence Virtuoso Não Resultados Esquemático adequados? Captura de esquemático Cadence Spectre Mentor Calibre Simulações Extração de no domínio do ter parasitas, DRC e LVS Sim Não Cadence Layout XL Resultados adequados? Layout

Figura 24 – Fluxo de projeto de ASIC com UMC e ferramentas *Cadence*.

Fonte: Autora (2023).

O uso da tecnologia UMC 180 nm faz parte de um programa da *EUROPRACTICE IC Service*, que oferece um custo reduzido na fabricação de ASICs para universidade e laboratórios de pesquisas (DAS; MCLEAN, 2003). Para reduzir o custo da fabricação a área é reduzida em um tamanho suficiente para a maioria dos projetos com fins acadêmicos, resultando em *mini ASICs*. Muitas tecnologias participam desse programa, dentre elas a UMC, que disponibiliza um custo reduzido para uma área de  $1,525 \times 1,525 \mu$ . A tecnologia *UMC* 180 nm é utilizada com o fluxo de ferramentas da *Cadence*.

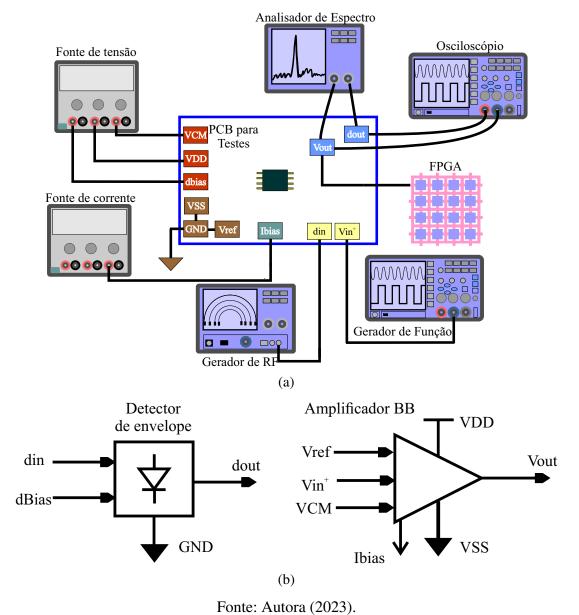

## 3.2.3 Setup para teste experimental dos ASICs

Após a submissão do CI para fabricação, o plano de testes é elaborado para realização dos testes experimentais. A Figura 25 ilustra o *setup* para medição dos resultados experimentais após o *chip* ser fabricado.

Figura 25 – Plano de testes: (a) Ilustração do setup de medição, (b) Indicação dos pinos do chip.

A Figura 25b faz a indicação dos pinos de entradas e saídas, e estes são descritos abaixo:

- din: sinal de entrada do detector de envelope;

- dBias: tensão de polarização (VGS) do transistor N do detector;

- dout: sinal de saída do detector;

- GND: tensão de referência em 0 V;

- Vref: entrada inversora do amplificador;

- Vin+: sinal de entrada do amplificador;

- VCM: tensão de modo comum;

- *Ibias*: corrente de polarização do OTA;

- VSS: tensão de alimentação do negativa do amplificador, conecata ao GND;

- VDD: alimentação positiva do amplificador;

- *Vout*: Sinal de saída do amplificador.

De modo geral, para os testes experimentais serão necessários os equipamentos ilustrados na Figura 25a e listados a seguir:

- Fonte de tensão para polarizar o transistor do detector (dBias), alimentar o amplificador (VDD) e fornecer a tensão de modo comum (VCM);

- Fonte de corrente para suprir a corrente de polarização do OTA;

- Osciloscópio para visualização dos sinais de entrada e saída no domínio do tempo;

- Analisador de espectro para avaliar os sinais de entrada e saída no domínio da frequência;

- FPGA para fazer a conversão do sinal analógico para digital e implementar a demodulação;

- Gerador de funções para produzir sinais de entrada para teste do amplificador;

- Gerador de RF será utilizado para gerar os sinais em altas frequências na entrada do receptor.

#### 3.3 Resumo do capítulo

Este capitulo descreveu sobre o sistema proposto e metodologia aplicada. Na primeira seção foi explicado sobre os circuitos avaliados para projeto do detector de conversão direta de ultra baixo consumo. As etapas da realização dessa pesquisa, bem como os fluxos de projetos empregados no desenho do ASIC foram explicados na seção 3.2. O fluxo de projeto da *SkyWater* é descatado pela interoperabilidade na utilização de diferentes ferramentas ao longo de cada etapa do fluxo de projeto. Além disso, foi ilustrado o *setup* para medição do *chip* quando fabricado. Após essas considerações, o capítulo 4 apresentará os resultados alcançados, as discussões e um comparativo com os trabalhos encontrados no estado da arte.

### 4 RESULTADOS E DISCUSSÕES

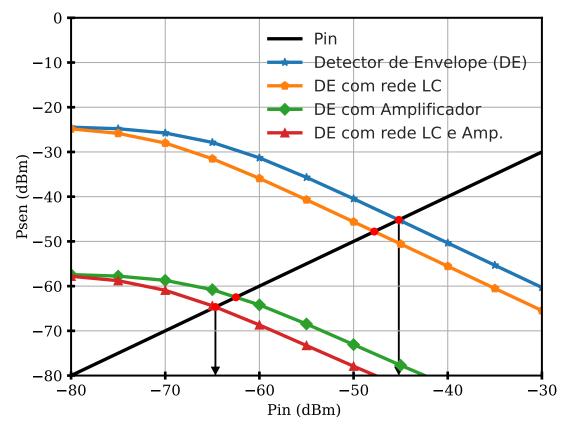

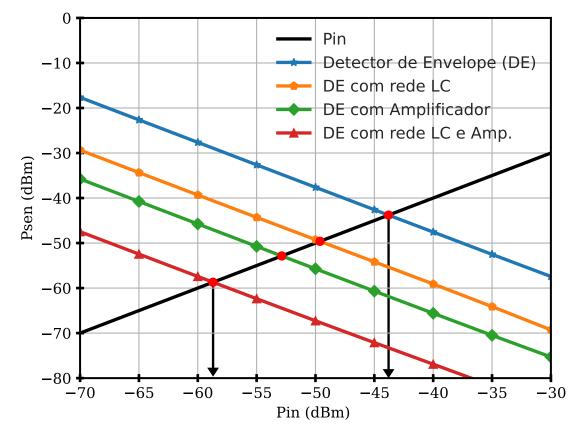

Este capítulo apresenta os resultados em nível de modelagem, simulações e *layout*. Os resultados foram obtidos utilizando as tecnologias CMOS *SkyWater* 130 nm e UMC 180 nm, assim como as respectivas ferramentas de cada fluxo de projeto. Para ambas as tecnologias, as curvas para implementação do método gm/Id foram geradas e os transistores foram dimensionados considerando as regiões de inversão.

Este capítulo está organizado em seções e em cada seção os resultados existe subseções que exibem os resultados para cada tecnologias separadamente. Na primeira seção serão mostrados os resultados para o detector de envelope passivo, na segunda seção será discutido sobre o amplificador com acoplamento capacitivo, a determinação da sensibilidade será exposta na terceira seção. Posteriormente o MODEM ASK será mostrado e por fim, os resultados serão contextualizados e comparados com os encontrados na literatura.

# 4.1 Detector de Envelope

Na primeira seção serão apresentados os resultados para o detector de envelope, iniciando com as simulações realizadas com as ferramentas do fluxo da tecnologia *SkyWater* 130 nm e seguindo com os resultados para a tecnologia UMC 180 nm. Uma subseção com discussões sobre os resultados também será exibida.

#### 4.1.1 Resultados para a tecnologia CMOS SkyWater 130 nm

Para a tecnologia *SkyWater* 130 nm, o detector foi simulado com uma tensão de *gate* de 0,8 V. O transistor do tipo N possui dimensões W/L de 9  $\mu$ m/0,15  $\mu$ m e o mínimo comprimento do canal foi utilizado para operação em alta frequência. Para esta tecnologia, os modelo dos MOSFETs é BSIM 4.

Em relação aos componentes passivo, a capacitância de entrada possui um valor de 15 pF e o filtro RC na saída possui uma resistência de  $100~K\Omega$  e capacitância de 0,985~pF, o que resulta em uma frequência de corte de aproximadamente 1,6~MHz.

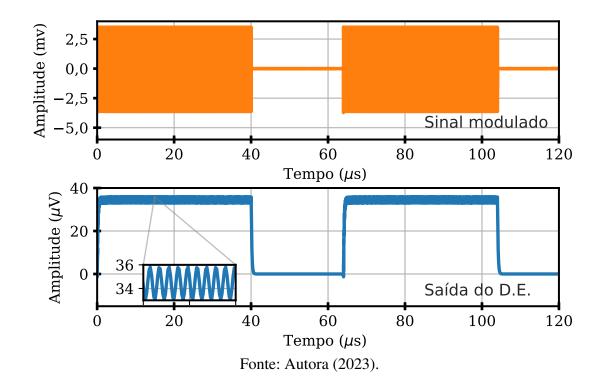

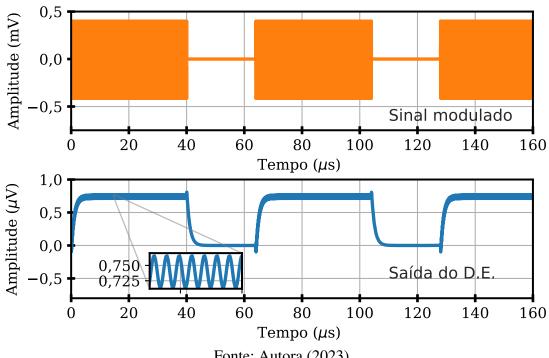

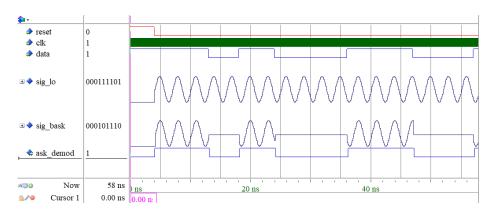

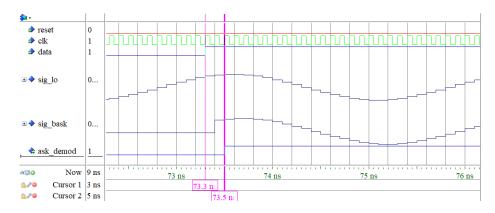

Para verificação comportamental do detector de envelope, foram realizadas a simulação transiente, ruído e ganho de conversão. Considerando um sinal modulado ASK com a portadora operando na banda *ISM* (do inglês *Industrial Scientific and Medical*)) em 2,45 *GHz*, a Figura 26 exibe a resposta transiente realizada por meio do *NgSpice* com os modelos da tecnologia *SkyWater* 130 nm.

Figura 26 – Análise transiente do detector para tecnologia SkyWater 130 nm.

Percebe-se que o detector de envelope faz a detecção da envoltória do sinal modulado ASK, realizando a etapa de *down conversion* do sinal de radio frequência na entrada. Como esperado, o sinal banda-base na saída é fortemente atenuado. A densidade espectral de potência do ruído na saída do detector pode ser observada na Figura 27.

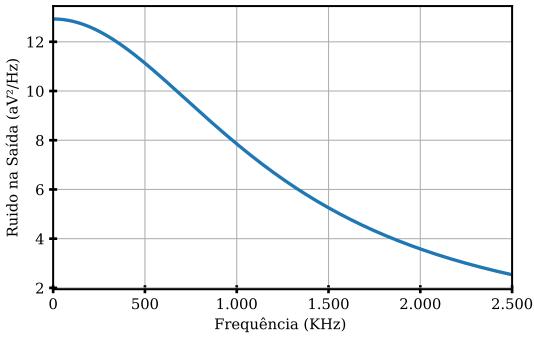

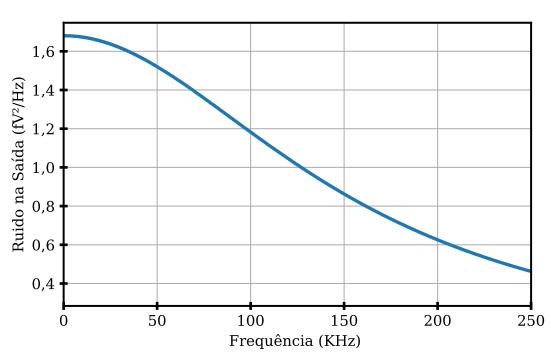

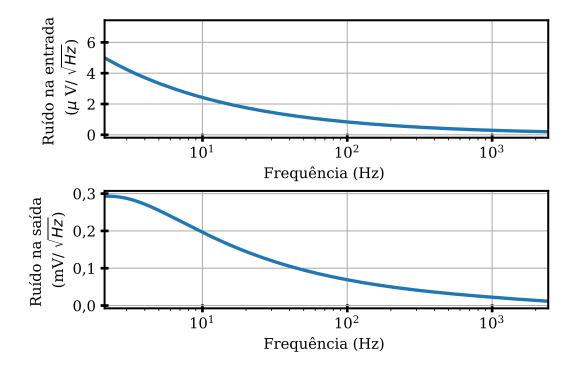

Figura 27 – Densidade espectral de potência do ruído na saída do detector.

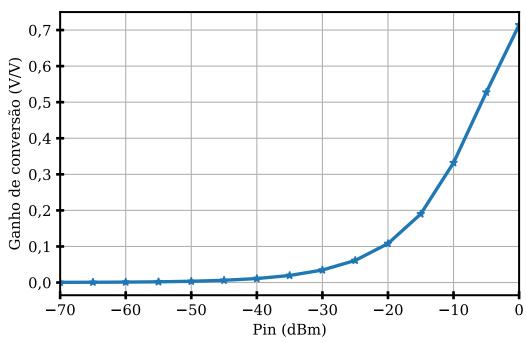

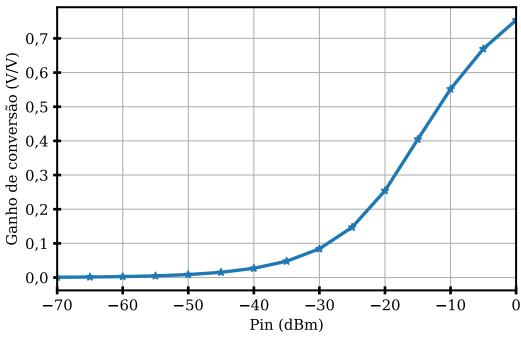

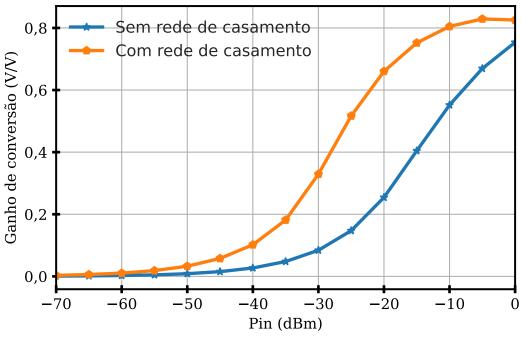

A potência espectral do ruído (unidade em  $V^2/Hz$ ) foi escolhida para fins comparativos. A amplitude do ruído espectral gerado ao longo da banda, é menor em comparação com o resultado obtido em Cheng e Chen (2017). Para determinação da figura de ruído, o ruido foi integrado ao longo da banda, considerando a largura de banda do ruído, com o fator de *brick wall*, conceito discutido no capítulo 2. O ruído total integrado ao longo da banda foi de 17,84  $pV^2$ . O ganho de conversão do detector também foi avaliado, considerando o valor *RMS* da tensão de saída pelo valor *RMS* sinal de entrada. A Figura 28 apresenta esse resultado com unidade em (V/V).

Figura 28 – Ganho de conversão para o detector da tecnologia *SkyWater*.

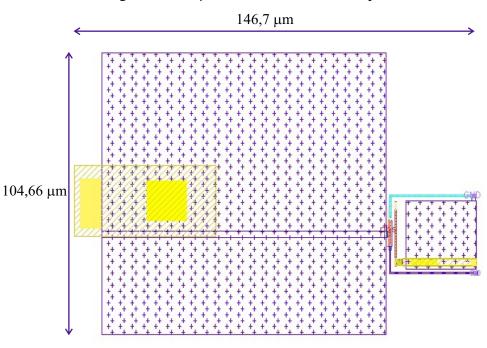

Após realizar as simulações pré-*layout*, o *layout* do detector foi desenhado com a ferramenta *Magic Layout*, considerando as regras de projeto e modelos da *Skywater* 130 nm. A Figura 29 exibe o *layout* do detector de envelope.

Figura 29 – *Layout* do detector de envelope.

Fonte: Autora (2023).

As dimensões do *layout* do detector são 146,  $7 \mu m \times 104$ ,  $66 \mu m$ , sendo a maior ocupação devido ao capacitor da entrada. O passo seguinte ao desenho do layout é a realização das simulações pós-*layout*. Nessas simulações as capacitâncias e resistências parasitas extraídas pela ferramenta Magic layout são consideradas. A Figura 30 mostra o ruído de saída do detector com os parasitas.

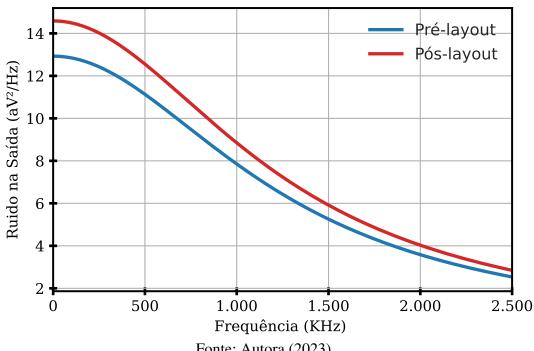

Figura 30 – Comparativo do ruído de saída pré e pós-layout.

Fonte: Autora (2023).

Os parasitas extraídos pelo Magic resultaram em uma aumento do ruído de saída para o detector. Contudo, o valor máximo permanece com bom desempenho. Na simulação pré-layout o valor máximo da potência do ruído é  $0.013 \ fV^2/Hz$ , enquanto na simulação pós-layout o valor é aproximadamente  $0.014 \ fV^2/Hz$ . Desse modo, o ruído total na saída do detector com as simulações pré-layout foi de 17,84  $pV^2$  e para as simulações pós-layout é 20,1  $pV^2$ . A Figura 31 apresenta o resultado para o ganho de conversão do detector.

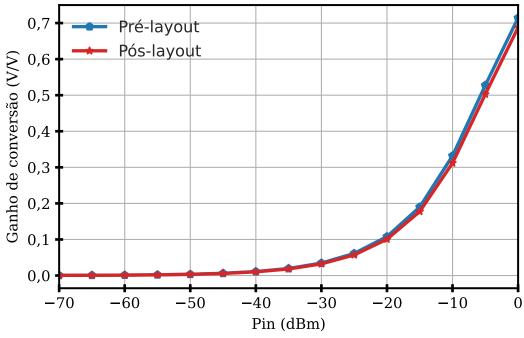

Figura 31 – Resultados pré e pós-layout para o ganho de conversão.

A Figura 31 traz os resultados para o ganho de conversão pré e pós-*layout*. De modo geral, pode-se afirmar que não houve alterações significativas na resposta, apenas uma pequena redução do ganho em alguns pontos.

### 4.1.2 Resultados com a tecnologia CMOS UMC 180 nm

Os mesmos resultados são exibidos para tecnologia UMC 180 nm com o modelo de transistores BSIM3V3, para essa tecnologia, o simulador *Spectre* foi utilizado. A Figura 32 exibe a análise transiente para o detector. O detector foi simulado com uma tensão de polarização de 0,5~V. Para operação em alta frequência o comprimento do canal do transistor é o mínimo. A relação W/L para o transistor é  $7~\mu m/0,18~\mu m$ . O capacitor de entrada foi ajustado para 10~pF, e o filtro RC na saída possui uma resistência de  $100~K\Omega$  e capacitância de 10~pF, na qual resulta em uma frequência de corte de 159~kHz.

Figura 32 – Análise transiente do detector para tecnologia UMC 180 nm.

A Figura 33 exibe o resultado simulado para o ruido na saída. O ruido gerado pelo detector da tecnologia CMOS UMC 180 nm foi maior do que o gerado pela tecnologia SkyWater 130 nm. No entanto, ainda possui um valor inferior ao trabalho de (CHENG; CHEN, 2017).

Figura 33 – Ruído na saída do detector da tecnologia UMC 180 nm.

Fonte: Autora (2023).

O valor máximo da potência do ruído ao longo da banda foi de  $1,6 \ fV^2/Hz$ . E o ruído integrado ao longo da banda foi de  $263,7 \ pV^2$ . A Figura 34 exibe o resultado simulado do ganho de conversão com o detector da tecnologia UMC 180 nm.

Figura 34 – Ganho de conversão para o detector da tecnologia UMC 180 nm.

Fonte: Autora (2023).

O detector projetado com a tecnologia UMC 180 nm apresentou um ganho de conversão um pouco maior em relação ao detector da *SkyWater* 130 nm, no entanto, deve-se considerar que os valor das capacitâncias são diferentes o que influência na impedância de entrada e largura de banda.

#### 4.1.3 Discussões a respeito dos resultados do detector de envelope

A partir do projeto dos detectores é possível inferir sobre as principais métricas para a sensibilidade de um receptor: seletividade e ruído. O ruído total para o detector da *SkyWater* 130 nm foi menor em comparação com o projeto da UMC 180 nm, enquanto que a largura de banda foi maior. A influência desse *trade-off* será exposta na seção 4.3. Os transistores foram polarizados considerando a tensão de limiar (ou *threshold*) para cada uma das tecnologias e o comprimento mínimo do canal foi utilizado para operação em mais alta frequência, para a tecnologia UMC o valor de 180 *nm* foi utilizado enquanto para a *SkyWater* o valor de 150 *nm* foi utilizado, embora o nome da tecnologia sugira que o nó do processo é 130 *nm* o comprimento mínimo é de 150 *nm*. Para a arquitetura de detector mostrada nessa pesquisa, as dimensões do transistor não tem influência no ganho de conversão.

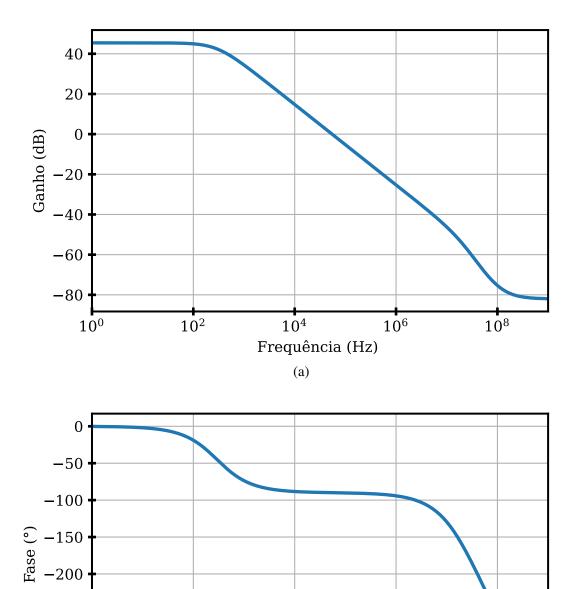

# 4.2 Amplificador com acoplamento CA